ADXL180

Rev. 0 | Page 45 of 56

DATA FRAME (18 BITS)

DATA

ADDRESS

P

TRANSMITTED

FIRST

START

STATE

2

1

0

2

1

0

0

1

BITS

VECTOR

2

1

0

7

6

5

4

3

0

3

07

54

4-

05

8

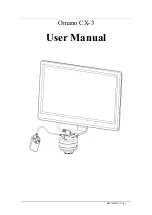

Figure 36. Configuration Mode Transmit Data Frame

CONFIGURATION MODE TRANSMIT

COMMUNICATIONS PROTOCOL

In configuration mode, the ADXL180 transmits the configura-

tion mode register data through the current mode Manchester

encoded serial port. The configuration mode protocol is fixed

regardless of the actual settings of the configuration registers

(RAM or OTP). The transmit communication protocol used by

the ADXL180 in configuration mode is

•

Manchester-1 data encoding

•

Two start bits (10b)

•

4-bit configuration mode register address field

•

8-bit configuration mode register data field

•

3-bit state vector field (101b)

•

One parity bit (even)

•

Synchronization pulse disabled

•

Auto-zero disabled

•

Data is transmitted LSB first

This is an 18-bit protocol (including the two start bits). Although

similar to the ADIFX protocol, it is different in that parity, and

not CRC, is used as the error checking code. This distinguishes

configuration mode messages from normal operation messages.

Figure 36 shows the configuration mode data frame format.

Table 42 shows the configuration mode transmit data bit mapping.

Excluding the two start bits, the word is 16 bits long. Data Bit

DB15 (transmitted last) is the parity bit. The configuration

mode transmit parity is even. The parity bit is set to either 1 or

0 to make the total number of 1s in the 16-bit word an even

number. Data Bits[DB14:DB11] are the four configuration

mode register address bits. The following eight data bits, DB10

through DB3, are the eight configuration mode register data

bits. The next three bits, DB2 through DB0, are the state vector

bits. In the configuration mode, the state vector is 101b. This

data frame format is different from the ADIFX format.