ADV8003 Hardware Manual

Rev. B, August 2013

146

Function

pvsp_enable_ffs

Description

0

Disable FFS/FRC

1

Enable FFS/FRC

3.2.1.1.

Autoconfiguration

Each block inside VIM and VOM can be automatically configured to reduce the configuration complexity. Two registers,

should be set to make the autoconfiguration work.

The 59.94/23.97 Hz timings have the same VID as the corresponding 60/24Hz timing in

pvsp_autocfg_input_vid[7:0]

, Primary VSP Map,

Address 0xE881[7:0]

This register is used to set the input timing VIC. If this register is 0, PVSP will use values in registers of pvsp_vin_h, pvsp_vin_v,

pvsp_is_i_to_p and pvsp_vin_fr to set input video.

Function

pvsp_autocfg_input_vi

d[7:0]

Description

0x06

Default: 480i@60

0xXX

Input timing VID

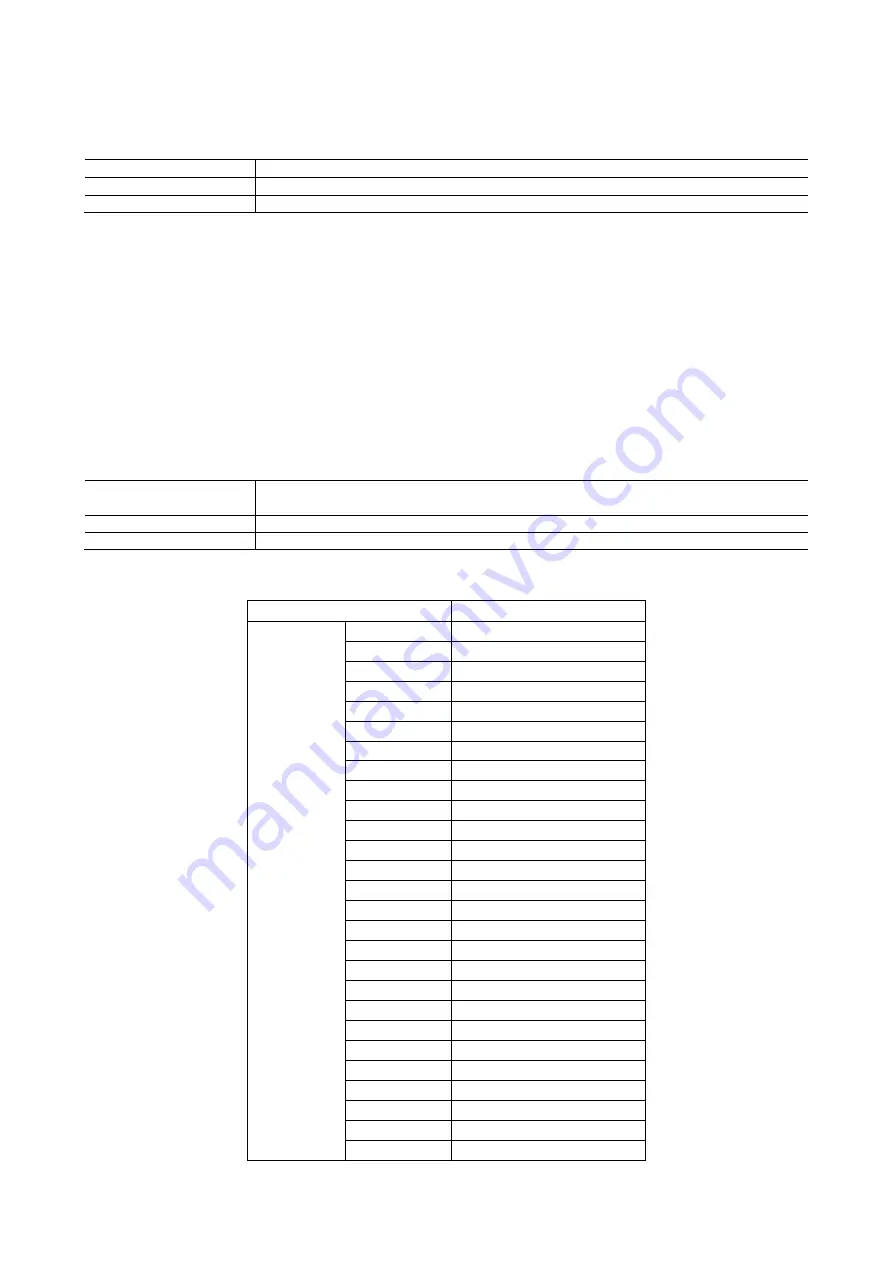

Table 22: PVSP Supported Input Video Timing and VID

Video Timing

VID

CEA

640x480p60

1

720x480p60

2 or 3 or 14 or 15 or 35 or 36

720x240p60

8 or 9 or 12 or 13

1280x720p60

4

1920x1080i60

5

720x480i60

6 or 7 or 10 or 11

1920x1080p

16

720x576p50

17 or 18 or 29 or 30 or 37 or 38

1280x720p50

19

1920x1080i50

20

720x576i50

21 or 22 or 25 or 26

720x288p50

23 or 24 or 27 or 28

1920x1080p50

31

1920x1080p24

32

1920x1080p25

33

1920x1080p30

34

1080i50-even

39

1080i100

40

720p100

41

576p100

42 or 43

576i100

44 or 45

1080i120

46

720p120

47

480p120

48 or 49

480i120

50 or 51

576p200

52 or 53

576i200

54 or 55

Summary of Contents for ADV8003

Page 366: ...ADV8003 Hardware Manual Rev B August 2013 366 Figure 144 ADV8003 Schematic Page 4...

Page 367: ...ADV8003 Hardware Manual Rev B August 2013 367 Figure 145 ADV8003 Schematic Page 5...

Page 368: ...ADV8003 Hardware Manual Rev B August 2013 368 Figure 146 ADV8003 Schematic Page 6...

Page 369: ...ADV8003 Hardware Manual Rev B August 2013 369 Figure 147 ADV8003 Schematic Page 7...

Page 371: ...ADV8003 Hardware Manual Rev B August 2013 371 Figure 149 ADV8003 Schematic Page 9...

Page 372: ...ADV8003 Hardware Manual Rev B August 2013 372 Figure 150 ADV8003 Schematic Page 10...

Page 373: ...ADV8003 Hardware Manual Rev B August 2013 373 Figure 151 ADV8003 Schematic Page 11...

Page 374: ...ADV8003 Hardware Manual Rev B August 2013 374 Figure 152 ADV8003 Schematic Page 12...

Page 375: ...ADV8003 Hardware Manual Rev B August 2013 375 Figure 153 ADV8003 Schematic Page 13...

Page 376: ...ADV8003 Hardware Manual Rev B August 2013 376 Figure 154 ADV8003 Schematic Page 14...

Page 377: ...ADV8003 Hardware Manual Rev B August 2013 377 Figure 155 ADV8003 Schematic Page 15...

Page 378: ...ADV8003 Hardware Manual Rev B August 2013 378 Figure 156 ADV8003 Schematic Page 16...

Page 379: ...ADV8003 Hardware Manual Rev B August 2013 379 Figure 157 ADV8003 Schematic Page 17...

Page 380: ...ADV8003 Hardware Manual Rev B August 2013 380 Figure 158 ADV8003 Schematic Page 18...

Page 381: ...ADV8003 Hardware Manual Rev B August 2013 381 Figure 159 ADV8003 Schematic Page 19...

Page 382: ...ADV8003 Hardware Manual Rev B August 2013 382 Figure 160 ADV8003 Schematic Page 20...

Page 383: ...ADV8003 Hardware Manual Rev B August 2013 383 Figure 161 ADV8003 Schematic Page 21...

Page 384: ...ADV8003 Hardware Manual Rev B August 2013 384 Figure 162 ADV8003 Schematic Page 22...

Page 385: ...ADV8003 Hardware Manual Rev B August 2013 385 Figure 163 ADV8003 Schematic Page 23...

Page 386: ...ADV8003 Hardware Manual Rev B August 2013 386 Figure 164 ADV8003 Schematic Page 24...

Page 387: ...ADV8003 Hardware Manual Rev B August 2013 387 Figure 165 ADV8003 Schematic Page 25...

Page 388: ...ADV8003 Hardware Manual Rev B August 2013 388 Figure 166 ADV8003 Schematic Page 26...

Page 389: ...ADV8003 Hardware Manual Rev B August 2013 389 Figure 167 ADV8003 Schematic Page 27...

Page 390: ...ADV8003 Hardware Manual Rev B August 2013 390 Figure 168 ADV8003 Schematic Page 28...

Page 391: ...ADV8003 Hardware Manual Rev B August 2013 391 Figure 169 ADV8003 Schematic Page 29...

Page 392: ...ADV8003 Hardware Manual Rev B August 2013 392 Figure 170 ADV8003 Schematic Page 30...

Page 393: ...ADV8003 Hardware Manual Rev B August 2013 393 Figure 171 ADV8003 Schematic Page 31...

Page 395: ...ADV8003 Hardware Manual Rev B August 2013 395 Figure 173 ADV8003 Layout Page 2...

Page 396: ...ADV8003 Hardware Manual Rev B August 2013 396 Figure 174 ADV8003 Layout Page 3...

Page 397: ...ADV8003 Hardware Manual Rev B August 2013 397 Figure 175 ADV8003 Layout Page 4...

Page 398: ...ADV8003 Hardware Manual Rev B August 2013 398 Figure 176 ADV8003 Layout Page 5...

Page 399: ...ADV8003 Hardware Manual Rev B August 2013 399 Figure 177 ADV8003 Layout Page 6...

Page 400: ...ADV8003 Hardware Manual Rev B August 2013 400 Figure 178 ADV8003 Layout Page 7...

Page 401: ...ADV8003 Hardware Manual Rev B August 2013 401 Figure 179 ADV8003 Layout Page 8...

Page 427: ...ADV8003 Hardware Manual Rev B August 2013 427 P 2 Z Z Z P 1 Z Z Z P 0 Z Z Z...