UG-191

AD9286-500EBZ User Guide

Rev. A | Page 4 of 24

DEFAULT OPERATION AND JUMPER SELECTION

SETTINGS

This section explains the default and optional settings or modes

allowed on the

evaluation board.

Power Circuitry

Connect the switching power supply that is supplied in the

evaluation kit between a rated 100 V ac to 240 V ac wall outlet

at 47 Hz to 63 Hz and J101.

Analog Input

The analog input on the evaluation board default configuration

uses a single transformer input with a 50 Ω impedance. The

default analog input configuration supports analog input fre-

quencies of up to ~200 MHz. This input network is optimized

to support a wide frequency band.

An alternate analog input configuration uses a single

ADA4937-1 ultralow distortion amplifier, which drives both

VIN1 and VIN2. Special attention has been paid to provide a

symmetrical layout between the two differential inputs to

realize best performance. To configure the analog input

circuitry, see Table 1.

The nominal input drive level is 10.5 dBm to achieve 1.2 V p-p full

scale into 50 Ω. At higher input frequencies, slightly higher input

drive levels are required due to losses in the front-end network.

VREF

The

operates with a fixed 1.0 V reference. This sets the

analog input span to 1.2 V p-p.

RBIAS

RBIAS has a default setting of 10 kΩ (R206) to ground and is

used to set the ADC core bias current. Note that using a resistor

value other than a 10 kΩ, 1% resistor for RBIAS may degrade

the performance of the device.

Clock Circuitry

The default clock input circuit on the

evaluation

board uses a simple transformer-coupled circuit using a high

bandwidth 1:1 impedance ratio transformer (T501) that adds a

very low amount of jitter to the clock path. The clock input is

50 Ω terminated and ac-coupled to handle single-ended sine wave

types of inputs. The transformer converts the single-ended input to

a differential signal that is clipped by CR501 before entering the

ADC clock inputs. The

board has on-chip circuitry to

distribute a single clock to each interleaved ADC channel.

Alternatively, the

evaluation board supports driving

each internal ADC core with its own separate half speed clock.

This is useful in applications where the user wants to externally

control the clock timing per channel. To enable separate

clocking, write a value 0 to SPI Address 0x09 and place a

jumper across J204 to tie AUXCLKEN to DRVDD.

Non-SPI Mode

For users who want to operate the DUT without using SPI,

remove the shorting jumpers on J302. This disconnects the

CSB, SCLK, and SDIO/PWDN pins from the SPI control bus,

allowing the DUT to operate in non-SPI mode. In this mode,

the SDIO/PWDN pin takes on an alternate function to enable

power-down functionality.

To enable the power-down feature, add a shorting jumper across

J202 at Pin 2 and Pin 3 to connect the SDIO/PDWN pin to

DRVDD.

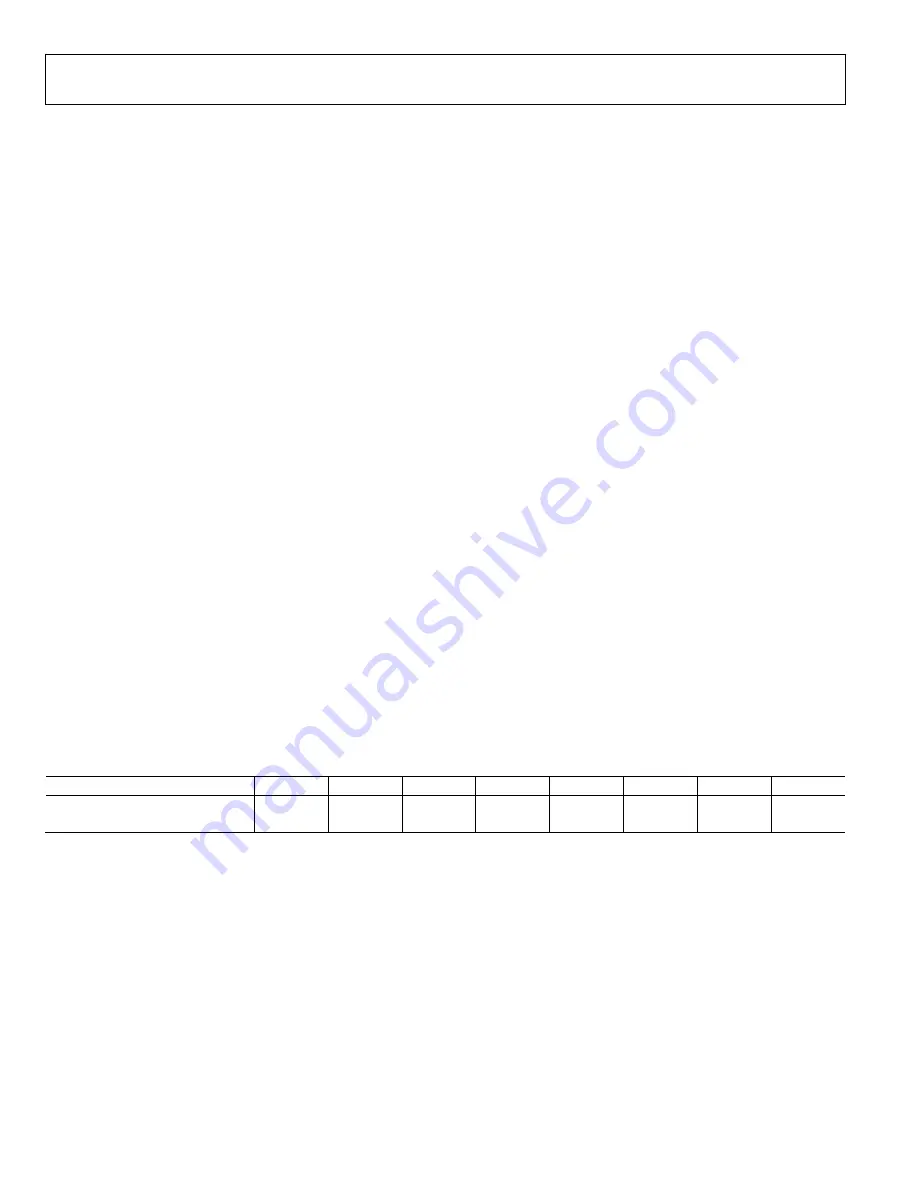

Table 1. Analog Input Mode Configurations

Analog Input Mode

R406

R407

R408

R409

R410

R411

R412

R413

Passive Path

DNI

0 Ω

0 Ω

DNI

33 Ω

33 Ω

33 Ω

33 Ω

Active Path

0 Ω

DNI

DNI

0 Ω

DNI

DNI

0 Ω

0 Ω

1

DNI = do not install.

Summary of Contents for AD9286-500EBZ

Page 6: ...UG 191 AD9286 500EBZ User Guide Rev A Page 6 of 24 09346 006 Figure 6 VisualAnalog Main Window...

Page 16: ...UG 191 AD9286 500EBZ User Guide Rev A Page 16 of 24 09346 020 Figure 20 Top Side...

Page 17: ...AD9286 500EBZ User Guide UG 191 Rev A Page 17 of 24 09346 021 Figure 21 Ground Plane Layer 2...

Page 18: ...UG 191 AD9286 500EBZ User Guide Rev A Page 18 of 24 09346 022 Figure 22 Power Plane Layer 3...

Page 19: ...AD9286 500EBZ User Guide UG 191 Rev A Page 19 of 24 09346 024 Figure 23 Power Plane Layer 4...

Page 20: ...UG 191 AD9286 500EBZ User Guide Rev A Page 20 of 24 09346 025 Figure 24 Ground Plane Layer 5...

Page 21: ...AD9286 500EBZ User Guide UG 191 Rev A Page 21 of 24 09346 025 Figure 25 Bottom Side...