– 34 –

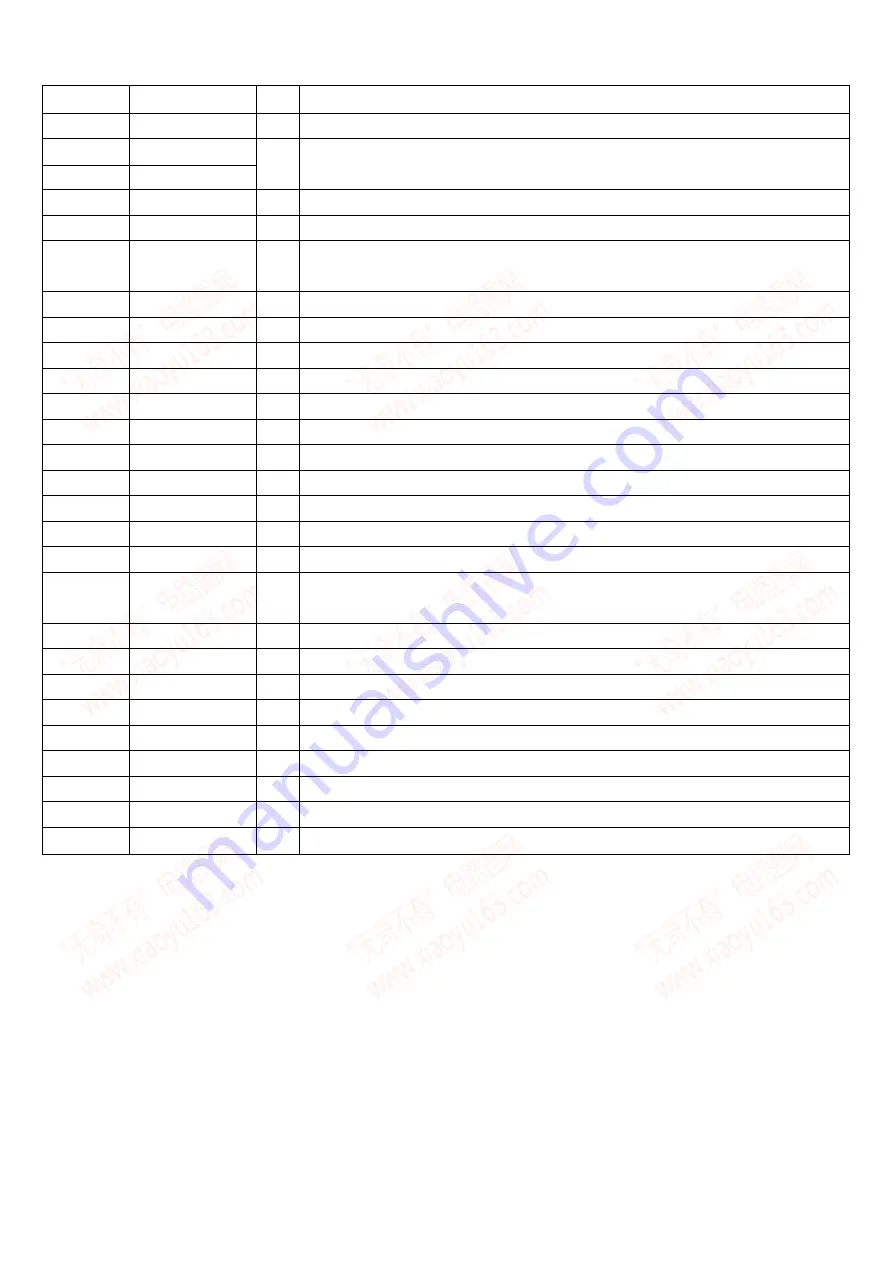

Pin No.

38

SLOF

I

Sled servo off control input.

39

CV–

I

CLV error signal input from the DSP.

40

CV+

41

RFSM

O

RF output.

42

RFS–

O

Sets the RF gain and the EFM signal's 3T compensation constant together with the RFSM pin.

43

SLC

O

The SLC (slice level control) signal is output to control the DSP's data slice level of the RF

waveform.

44

SLI

I

Input to control the DSP's data slice level.

45

D-GND

–

Ground of digital signals.

46

FSC

O

Output for the focus search smoothing capacitor.

47

TBC

I

The TBC (tracking balance control) signal sets the EF balance variation range.

48

NC

–

Not connected.

49

DEF

O

Disc defect detection output.

50

CLK

I

Reference clock input. 4.23MHz is input from the DSP.

51

CL

I

Microprocessor command clock input.

52

DAT

I

Microprocessor command data input.

53

CE

I

Microprocessor chip enable input.

54

DRF

O

DRF (detect RF) is an output to detect the RF level.

55

FSS

I

The FSS (focus search select) signal switches the focus search modes (+/-search / +search with

respect to the reference voltage). (Not used)

56

VCC2

–

VCC of servo and digital circuits.

57

REFI

–

For the connection of bypass capacitor for the reference voltage.

58

VR

O

Reference voltage output.

59

LF2

–

Sets the time constant for disc defect detection.

60

PH1

–

For the connection of a capacitor to hold the RF signal peak.

61

BH1

–

For the connection of a capacitor to hold the RF signal bottom.

62

LDD

O

APC circuit output.

63

LDS

I

APC circuit input.

VCC of RF signal circuits.

I/O

Description

Pin Name

www. xiaoyu163. com

QQ 376315150

9

9

2

8

9

4

2

9

8

TEL 13942296513

9

9

2

8

9

4

2

9

8

0

5

1

5

1

3

6

7

3

Q

Q

TEL 13942296513 QQ 376315150 892498299

TEL 13942296513 QQ 376315150 892498299