49

TXB2+

FSADDR5

C423

0.001uF

VDD_MPLL

FSDATAU0

FSDATAU23

AVDDA

3

FSCLK+

6

FSADDR0

FSDATAU25

TXB3-

FSDATAU11

FSDQSU1 6

+APLL

TXAC-

TXB3-

WR

AVDD_DVI

BIN

4

GND

TXA3+

SOG

4

FSDATAU30

FSDATAU18

C428

0.1uF

TXA0+

FSADDR3

FSADDR4

FSDATAU5

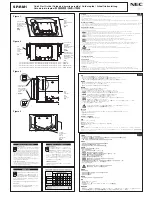

MST9251A(208Pin)

U401

168

167

166

165

164

161

160

180

179

178

177

176

175

174

131

205

44

43

42

41

40

39

38

37

18

15

14

11

9

8

6

5

26

25

24

23

22

21

20

19

1

208

2

3

207

36

33

32

31

30

29

28

27

45

46

47

48

80

49

51

54

55

10

34

173

17

195

125

109

86

56

204

113

156

58

59

60

61

16

35

12

50

57

157

64

183

184

7

132

155

172

158

169

185

102

4

87

170

171

108

159

140

13

62

67

68

69

70

71

72

73

74

75

76

78

201

135

136

137

138

141

142

143

144

145

146

147

148

149

150

151

152

133

105

107

110

111

112

115

116

117

118

119

120

121

122

123

124

127

128

129

65

181

186

187

66

63

202

203

163

52

53

103

77

81

82

83

84

85

154

114

88

89

90

91

92

93

126

139

94

95

96

97

98

99

100

101

106

104

130

134

153

200

79

206

162

194

182

188

189

190

191

192

193

196

197

198

199

LVA1P

LVA2M

LVA2P

LVACKM

LVACKP

LVA3M

LVA3P

LVB1P

LVB2M

LVB2P

LVBCKM

LVBCKP

LVB3M

LVB3P

VDDC

GND

VI_DATA[11]

VI_DATA[10]

VI_DATA[9]

VI_DATA[8]

REFM

REFP

RMID

VSYNC0

HSYNC1

DDCD_CK

DDCD_DA

REXT

DVI_CK-

DVI_B-

DVI_B+

RIN1M

RIN1

GIN1M

GIN1

SOGIN1

BIN1M

BIN1

VSYNC1

GND

DVI_R-

DVI_G+

DVI_G-

DVI_R+

HSYNC0

RIN0

RIN0M

SOGIN0

GIN0

GIN0M

BIN0

BIN0M

VI_DATA[12]

VI_DATA[13]

VI_DATA[14]

VI_DATA[15]

GND

AVDD_

APL

L

GPIO[5]/VHS

VI_DATA[0]

VI_DATA[1]

AVDD_

DVI

AVDD_

ADC

VDDC

AVDD_

ADC

VDDC

VDDM

AVDD_

PL

L

2

VDDM

VI_DATA[2]

AVDD_

M

P

L

L

VDDM

VDDC

VI_DATA[4]

VI_DATA[5]

VI_DATA[6]

VI_DATA[7]

GND

GND

AVDD_

PL

L

GND

VI_DATA[3]

GND

GND

GND

GND

GND

GND

GND

GND

BYPASS

LVA1M

VDDC

VDDM

AVDD_

DVI

GND

LVA0P

LVA0M

GND

GND

GND

GND

VCTRL

HWRESET

INT

ALE

RDZ

WRZ

DBUS[0]

DBUS[1]

DBUS[2]

DBUS[3]

GPIO[3]/VDE

GPIO[1]/FIELD

PWM1

MDATA[15]

MDATA[14]

MDATA[13]

MDATA[12]

MDATA[11]

MDATA[10]

MDATA[9]

MDATA[8]

MDATA[7]

MDATA[6]

MDATA[5]

MDATA[4]

MDATA[3]

MDATA[2]

MDATA[1]

MDATA[0]

DQM[0]

MCLKE

MCLK

BADR[1]

BADR[0]

RASZ

CASZ

WEZ

MADR[0]

MADR[1]

MADR[2]

MADR[3]

MADR[4]

MADR[5]

MADR[6]

MADR[7]

MADR[8]

MADR[9]

MADR[10]

GND

LVB1M

LVB0P

LVB0M

VDDP

VDDC

XOUT

XIN

GND

GPIO[4]/VCLK2

VI_CK

GND

GPIO[2]/VVS

DQS[3]

MDATA[31]

MDATA[30]

MDATA[29]

MDATA[28]

VDDM

GND

MDATA[27]

MDATA[26]

MDATA[25]

MDATA[24]

MDATA[23]

MDATA[22]

GND

VDDM

MDATA[21]

MDATA[20]

MDATA[19]

MDATA[18]

MDATA[17]

MDATA[16]

DQS[2]

DQM[1]

MCLKZ

MVREF

MADR[11]

DQS[1]

DQS[0]

PWM0

VDDC

GND

VDDP

GND

VDDP

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

MCU

I

N

TE

RFACE

AD1

FSDQM1

6

FSDQM0

6

FSDQSU3 6

WR

7

TXB3+

AD2

C425

0.1uF

GIN

4

GND

FSDATAU27

G-

4

FSBKSEL0 6

FSDATAU7

FSDATAU3

R+

4

FSDQSU2 6

FSCLK-

FSADDR[0..11]

TXA0-

B+

4

R

465

360

1/10W

INT

7

TXBC-

AD2

XTAL

+3.3DV2

TXB1+

FSDATAU2

GNDG

4

AD3

TXB2-

HWRESET

TXB2+

RX0+

Unloaded trace impedance on this interface is 90 Ohm

Loaded trace impedace with DRAM load is 65 Ohm (for 2.5 inch total trace

length)

AVDD_PLL

TXAC-

+2.5MVDD

3

R-

4

FSCLK+

FSDQM0U

TXAC+

RX0-

AD0

7

TXB0+

RX1+

FSDATAU16

R443

10K 1/16W

AdjBACKLITE

3

R449

33 1/16W

VDDC

FSDATAU8

ALE

+

C424

22uF/50V

TXA2+

ALE

7

FSBKSEL0

FSADDR11

R444

390 1/16W

GNDR

4

FSDQSU0 6

VSYNC

4

FSDATAU14

RD

TXB0-

TXA3-

AD0

FSDATAU10

FSADDR1

C418

22pF

AVDD_DVI

TXA2-

FSDATAU28

INT

CN407

CONN

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

AD2

7

R

447

360

1/10W

/FSRAS

6

RXC-

RXC+

R451

1K 1/16W

B-

4

(5mm)

R450

1K 1/16W

+3.3DV1

FSADDR8

TXA1+

TXA1-

FSADDR9

R

445

360

1/10W

ALE

RD

TXB1+

FSADDR6

FSDATAU22

C421

0.1uF

RX2+

VDD_MPLL

3

GNDB

4

FSDATAU[0..31]

6

FSBKSEL1 6

TXB2-

ADJ_PWM

L404

120 OHM

R

446

360

1/10W

DVI INPUT

AD1

7

TXBC-

FSDATAU12

HWRESET

PLL_GND

TXB0-

RX1-

FSDATAU13

C419

22pF

CLK+

4

GND

FSDATAU6

RD

7

FSDATAU17

MVref

FSADDR[0..11]

6

TXB1-

FSDATAU26

FSBKSEL1

FSDATAU4

CLK-

4

AD3

7

RX2-

FSDATAU31

AVDD_PLL

3

TXA2+

AD3

FSCKE

6

TXBC+

AD0

TXB1-

X401

14.318MHz

AVDDPLL2 3

/FSCAS

6

+2.5MVDD

Scaler (MST9251A)

1

715G1765-1 for AL2051W (acer)

C

5

8

Tuesday, January 03, 2006

Title

Size

Document Number

Rev

Date:

Sheet

of

/FSWE

VLCD

3

VLCD

TXA0-

FSDATAU9

+3.3DV1

3

FSCLK-

6

AVDDPLL2

GND

FSADDR10

R448

33 1/16W

AVDD_DVI

3

FSADDR7

FSCLK+, FSCLK- should be routed

like a differentail pair

TXA3-

TXA1-

/FSRAS

TXAC+

FSDATAU19

/FSCAS

HSYNC

4

INT

TCLK

FSDATAU15

TXB0+

FSDATAU21

+2.5MVDD

G+

4

TXA3+

FSDATAU1

C422

0.1uF

VDDC

3

TXA0+

R442

100 1/16W

For AOC LCD I/F-

F/W default set Odd/Even Swap.

4/13/93

TXA1+

HWRESET

7

AVDDA

GND

Volume

8

CONNECTOR for PANEL

TXB3+

WR

MVref

FSDATAU[0..31]

MVref

C420

0.1uF

FSCKE

+3.3DV2

3

VGA

INPUT

FSDATAU24

FSDATAU29

TXA2-

TXBC+

RIN

4

AD1

FSADDR2

R

466

360

1/10W

C427

0.1uF

MVref

+APLL

3

FSDATAU20

FSDQM1U

/FSWE

6

Summary of Contents for AL2051

Page 1: ...1 Acer AL2051W Service Guide ...

Page 22: ...22 b The Description For Control Function ...

Page 23: ...23 ...

Page 42: ...42 Exploded Diagram Model AL2051W ...

Page 53: ...53 Power Inverter board ...