RFSoC Data Converter Evaluation Tool User Guide

7

UG1287 (v2018.2) October 1, 2018

Chapter 1:

Introduction

Zynq Ult RFSoC Overview

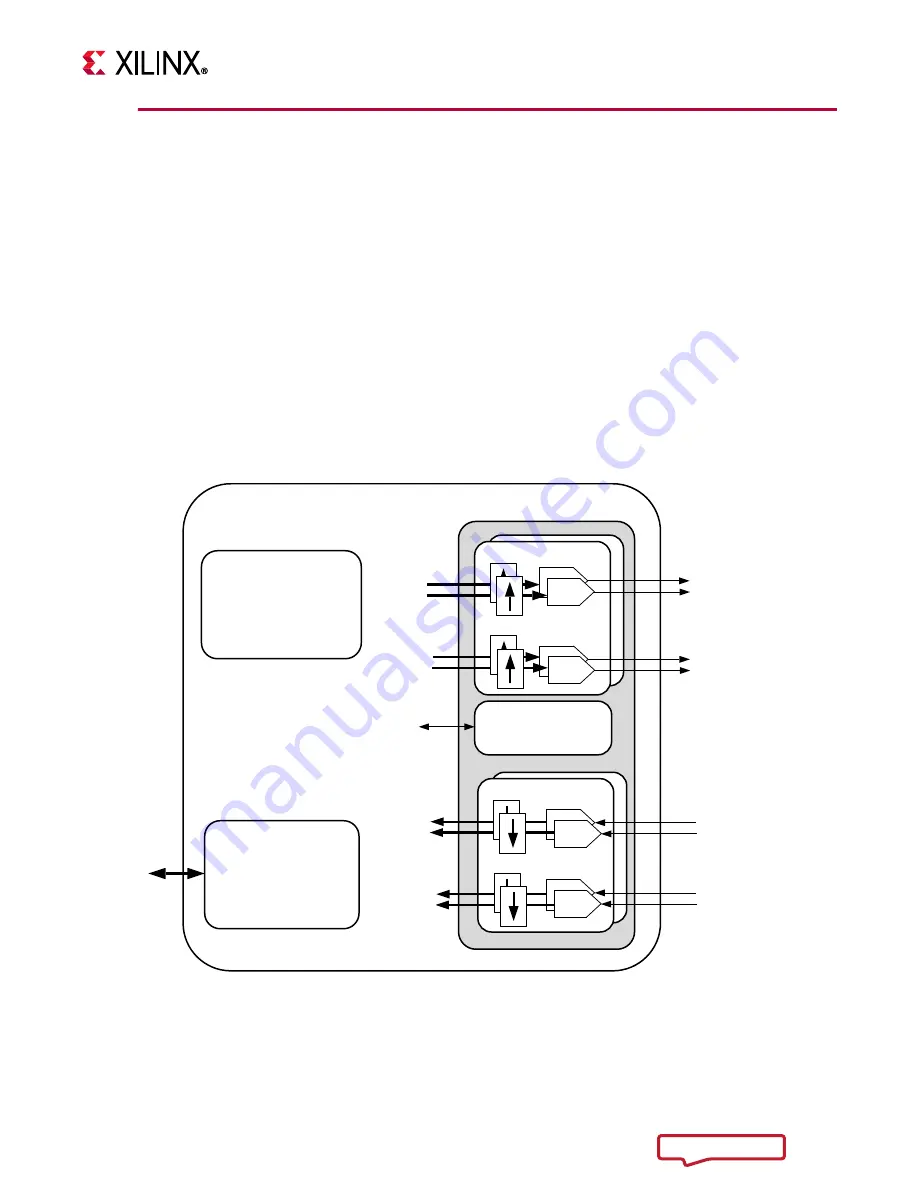

The Zynq Ult RFSoC family integrates the key subsystems required to implement a

complete software-defined radio including direct RF sampling data converters, enabling

CPRI and Gigabit Ethernet-to-RF on a single, highly programmable SoC.

Each RFSoC offers multiple RF-sampling analog-to-digital (RF-ADC) and RF-sampling

digital-to-analog (RF-DAC) data converters. The RF-ADC supports a maximum sample rate

of 4 GSPS with dynamic range and has a signal bandwidth of up to 4 GHz. The RF-DAC can

clock at up to 6.554 GSPS with an output signal bandwidth of greater than 4 GHz. The RF

data converters also include power efficient digital down converters (DDCs) and digital up

converters (DUCs) that include programmable interpolation, decimation rates, a

numerically controlled oscillator (NCO), and a complex mixer. The DDCs and DUCs can also

support multi-band operation.

shows the block diagram of the Zynq Ult

RFSoC RF Data Converter.

X-Ref Target - Figure 1-1

Figure 1-1:

Zynq Ult RFSoC RF Data Converter in RFSoC

Zynq Ult RFSoC

Control and

Configuration

Data Converter IP Core

Processing System

Quad ARM Cortex-A53

Dual ARM Cortex-R5

GTY Serial

Transceivers

Programmable

Logic

DUC

AXI4-Stream

DUC

AXI4-Stream

8 TX Channels

DDC

AXI4-Stream

DDC

AXI4-Stream

8 RX Channels

AXI4-Lite

DAC

DAC

ADC

ADC

X21232-092118