VCU1287 IBERT Getting Started Guide

13

UG1203 (v2016.4) December 15. 2016

Chapter 1:

VCU1287 IBERT Getting Started Guide

Starting the SuperClock-2 Module

The SuperClock-2 module features two clock-source components:

• Always-on Si570 crystal oscillator

• Si5368 jitter-attenuating clock multiplier

Outputs from either source can be used to drive the transceiver reference clocks.

To start the SuperClock-2 module:

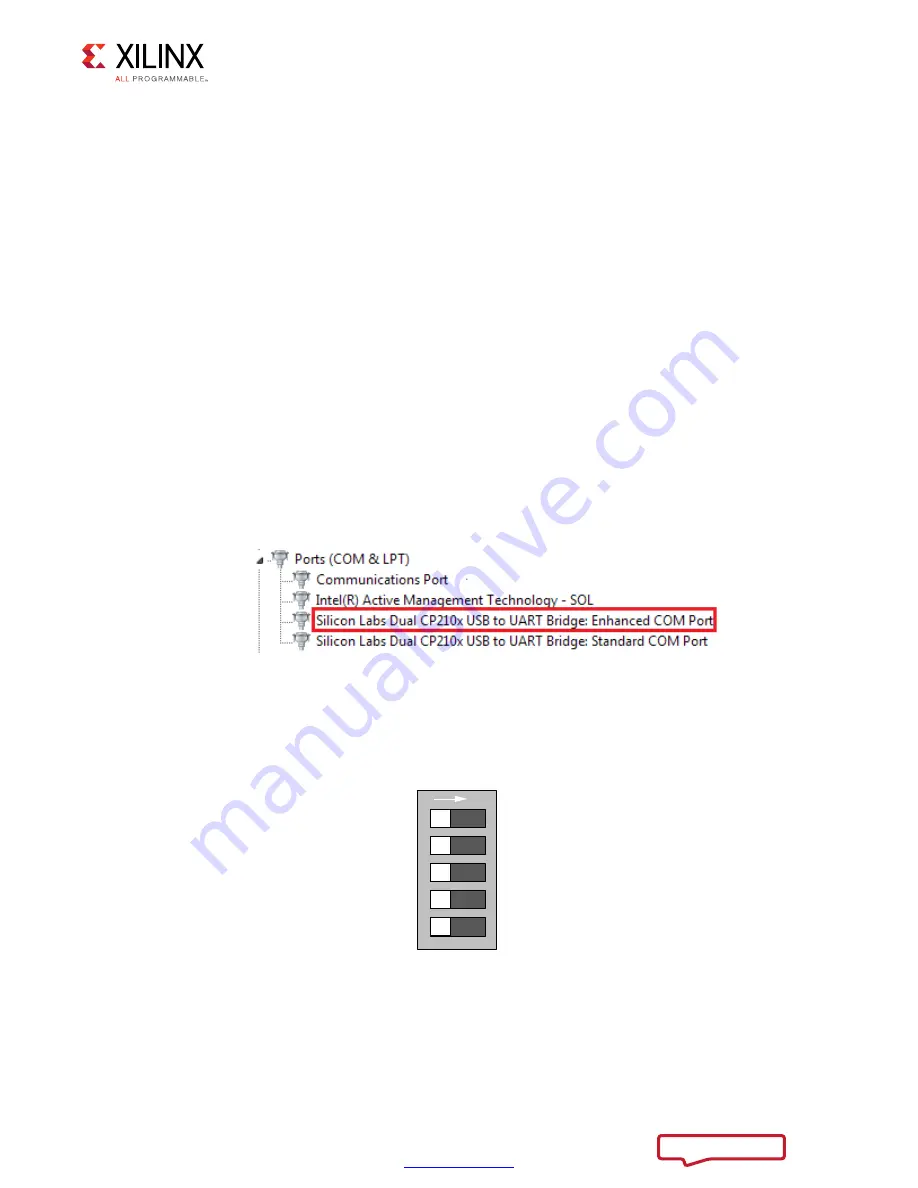

1. The SuperClock-2 module is configured using the Xilinx XC7Z010CLG225

Zynq-7000APSoC System Controller command line which can be accessed through a

serial communication terminal connection using the enhanced communication port of

the Silicon Labs USB to Dual UART Bridge (

). Additional information about the

Silicon Labs USB-to-UART is available in

Silicon Labs CP210x USB-to-UART Installation

Guide

(UG1033)

Review the

VCU1287 Evaluation Board User Guide

(UG1120)

for additional

information about the System Controller.

2. Set the System Controller configuration DIP switches (SW13) to the OFF position

(

). This disables configuration of the FPGA at power reset.

X-Ref Target - Figure 1-9

Figure 1-9:

Silicon Labs Enhanced COM PORT

X-Ref Target - Figure 1-10

Figure 1-10:

Configuration DIP Switch (SW13)

X15548-121416

ENABLE

ADDR0

ADDR1

ADDR2

ADDR3

ON

X15549-121416