74

Virtex-6 FPGA Connectivity Kit Getting Started

UG664 (v1.4) July 6, 2011

Getting Started with the Virtex-6 FPGA IBERT Reference Design

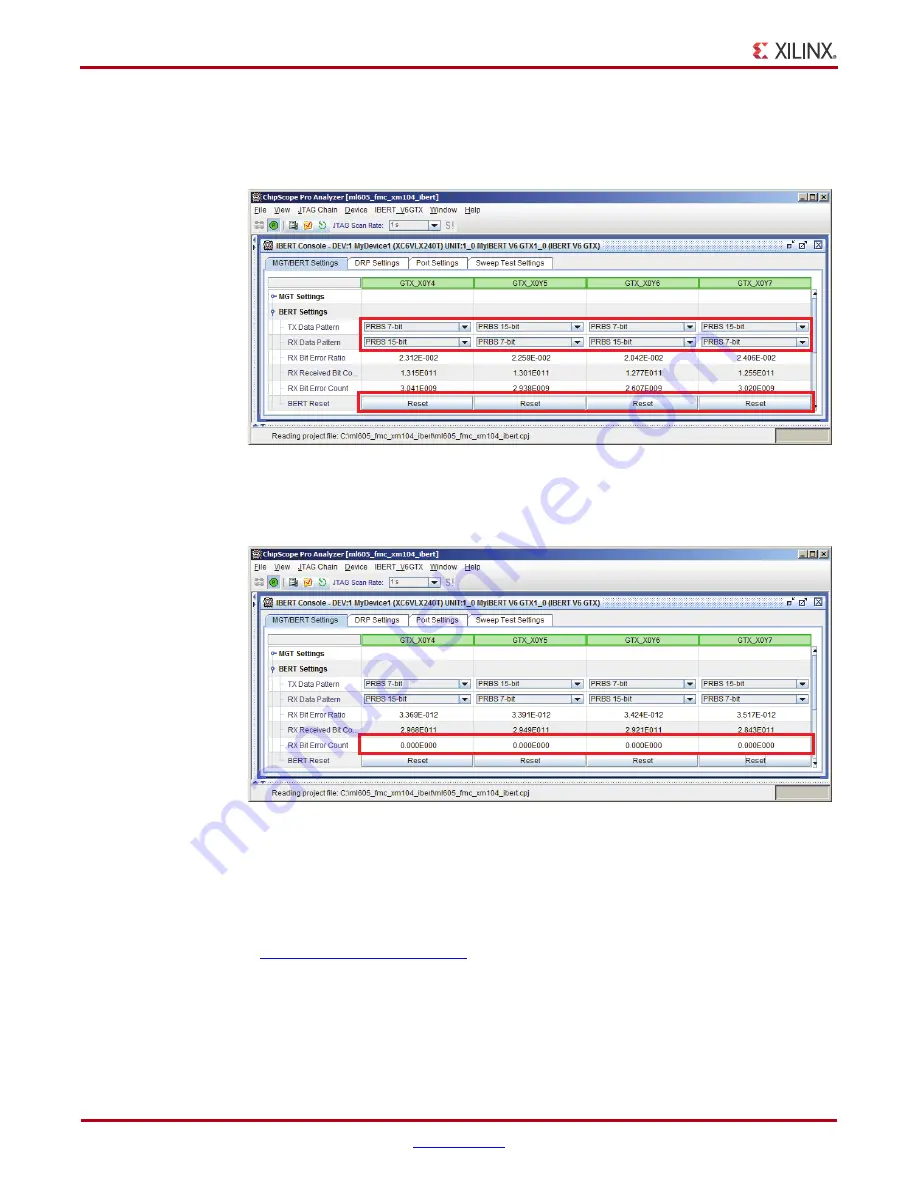

15. Configure the bit error ratio test (BERT) parameter settings (see

a.

Set the TX/RX data patterns to PRBS 7-bit and 15-bit.

b. Click the BERT

Reset

buttons for each channel.

16. View the reported BERT (see

). The RX bit error count should be 0.

Congratulations! The IBERT reference design for the Virtex-6 FPGA Connectivity Kit has

been set up and the pre-built demo that uses the GTX transceivers running at 3.125 Gb/s

has been tested.

For further details on other example reference designs available for the ML605 board, refer

to

and click on

ML605 Documentation

.

X-Ref Target - Figure 78

Figure 78:

Configuring the BERT Settings for the GTX Transceiver Channels

X-Ref Target - Figure 79

Figure 79:

Verify the Bit Error Ratio on All Four Transceiver Channels

UG664_55_021810

UG664_56_021810

Содержание Virtex-6 FPGA

Страница 1: ...Virtex 6 FPGA Connectivity Kit Getting Started Guide UG664 v1 4 July 6 2011 XPN 0402826 03...

Страница 4: ...Virtex 6 FPGA Connectivity Kit Getting Started www xilinx com UG664 v1 4 July 6 2011...

Страница 6: ...6 www xilinx com Virtex 6 FPGA Connectivity Kit Getting Started UG664 v1 4 July 6 2011...