Using an EDIF software flow

143

Using the Xilinx Software

were generated in Simulink. Provided that your design was error free, the ModelSim

console window will report that the simulation finished without errors.

Your installed version of ModelSim (either MXE or ModelSim EE/SE/PE) must be

associated with the Project Navigator tool for this interaction to work. To associate

ModelSim with the Project Navigator, follow the instructions in the Simulation

section, later in this chapter.

Using an EDIF software flow

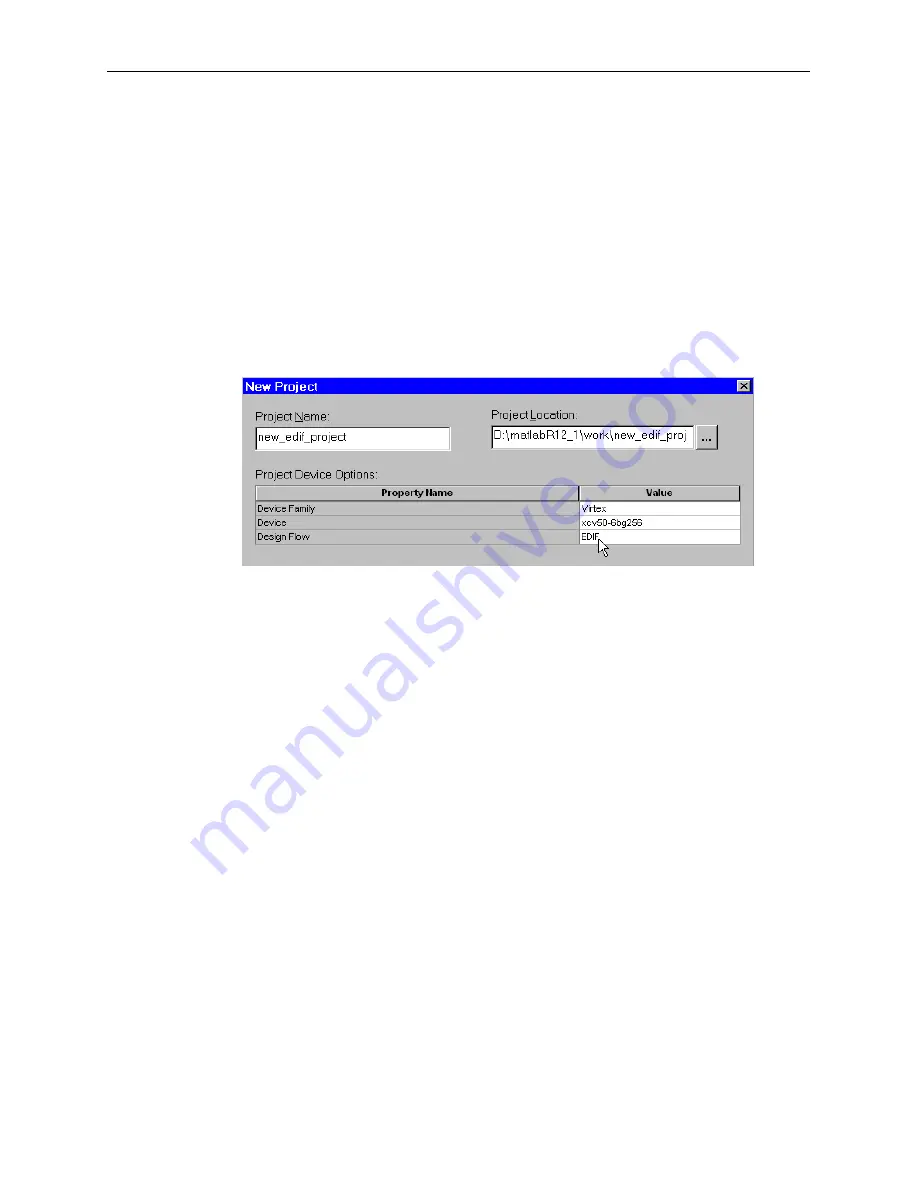

You may not wish to use the Project Navigator for your VHDL synthesis. If you

choose to run a synthesis compiler in a standalone software tool, then you will

generate EDIF. You may wish to import your EDIF files into the Project Navigator.

To do this, open the Project Navigator and select

File >> New Project

. A new

project properties dialog will open. Select EDIF as the design flow type.

Figure 5-8: EDIF design flow in Project Navigator

Now you may add your EDIF files to the project as sources. From the Project

Navigator pulldown menu bar, choose

Project>>Add Source

, and then browse to

your EDIF files.

Simulation

The System Generator creates custom .

do

files for use with your generated project and

a ModelSim simulator. To use these files, you must have ModelSim (PE or EE/SE) or

the Xilinx Edition of ModelSim (MXE). You may run your simulations from the

standalone ModelSim tool, or you may associate it with the Xilinx 4.1i ISE Project

Navigator, and run your simulations from within Project Navigator as part of the full

software implementation flow.

Compiling your IP

You must compile your IP (cores) libraries with ModelSim before you can simulate.

ModelSim (PE or EE/SE)

To compile your IP with ModelSim (PE or EE/SE) you will need to download a TCL/

TK script from the Xilinx web site, and run it to compile these libraries:

Xilinx Simprim

Unisim

XilinxCoreLib