AXI Bridge for PCI Express v2.4

25

PG055 June 4, 2014

Chapter 2:

Product Specification

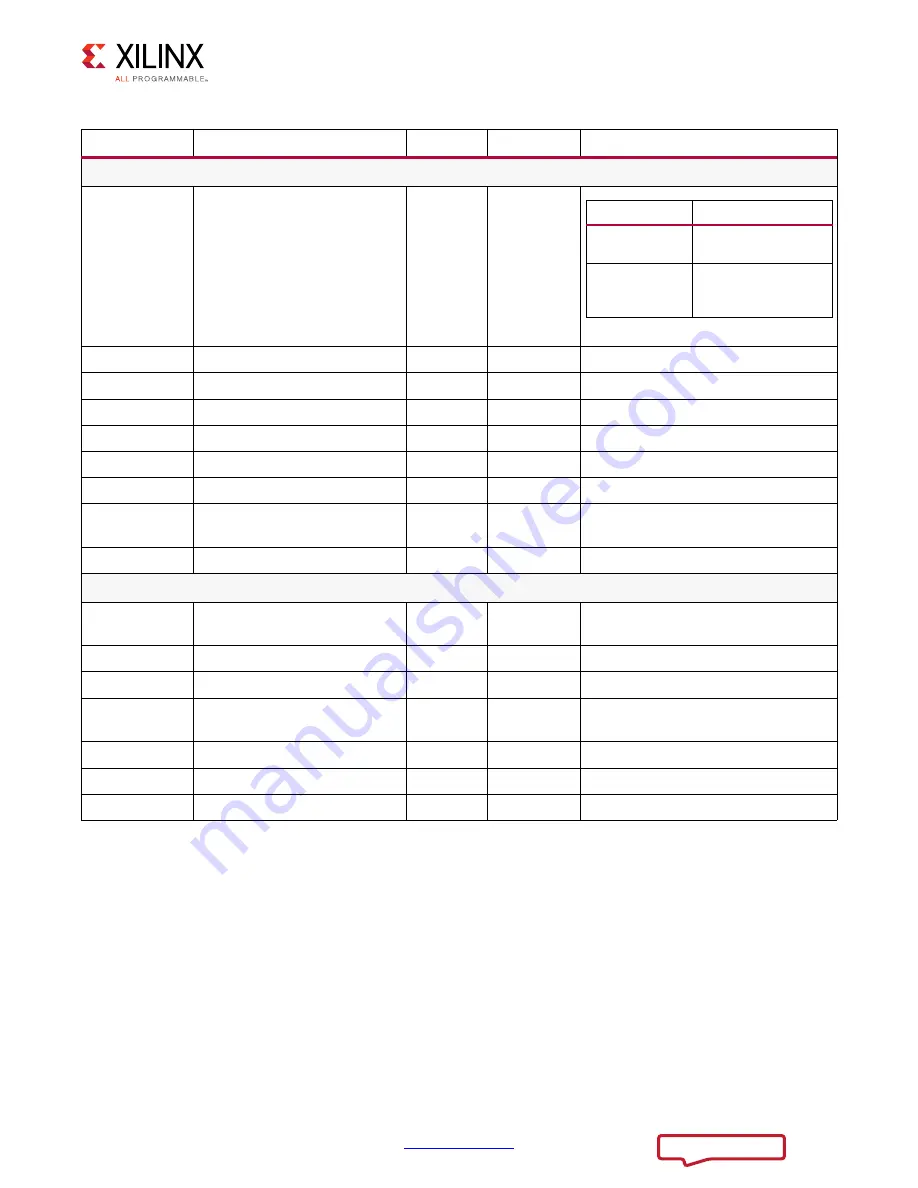

summarizes the relationship between the IP design parameters, C_FAMILY and

C_PCIE_USE_MODE. The C_PCIE_USE_MODE is used to specify the 7 series (and derivative

FPGA technology) serial transceiver wrappers to use based on the silicon version. Initial

Engineering Silicon (IES) as well as General Engineering Silicon (GES) must be specified.

Core for PCIe Configuration Parameters

G41

C_NO_OF_LANES

,

,

G42

C_DEVICE_ID

G43

C_VENDOR_ID

G44

C_CLASS_CODE

G45

C_REV_ID

G46

C_SUBSYSTEM_ID

G47

C_SUBSYSTEM_VENDOR_ID

G48

C_PCIE_CAP_SLOT_

IMPLEMENTED

If G2 = 0, G48 is not meaningful

G49

C_REF_CLK_FREQ

Memory-Mapped AXI4 Bus Parameters

G50

C_M_AXI_DATA_WIDTH

,

,

G50 must be equal to G53

G51

C_M_AXI_ADDR_WIDTH

G51 must be equal to G54

G52

C_S_AXI_ID_WIDTH

G53

C_S_AXI_DATA_WIDTH

,

,

G53 must be equal to G50

G54

C_S_AXI_ADDR_WIDTH

G54 must be equal to G51

G55

C_MAX_LINK_SPEED

G56

C_INTERRUPT_PIN

Table 2-5:

Parameter Dependencies

(Cont’d)

Generic

Parameter

Affects

Depends

Description

Parameter Setting

Result

G1 = Kintex-7 &

G50 = G53 = 64

G41 = 1, 2, or 4 (Gen1),

or G41 = 1 or 2 (Gen2)

G1 = Kintex-7 &

G50 = G53 = 128

G41 = 1, 2, 4, or 8

(Gen1) or 1, 2, or 4

(Gen2)