KC724 GTX Transceiver Characterization Board

27

UG932 (v2.2) October 10, 2014

Detailed Description

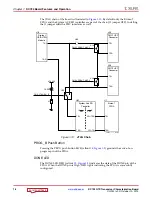

Information for each GTX transceiver clock input is shown in

.

F6

117_RX3_P

117

J85

2,873

F5

117_RX3_N

117

J85

2,872

D2

118_TX0_P

118

J86

2,842

D1

118_TX0_N

118

J86

2,844

E4

118_RX0_P

118

J86

3,048

E3

118_RX0_N

118

J86

3,049

C4

118_TX1_P

118

J86

2,629

C3

118_TX1_N

118

J86

2,628

D6

118_RX1_P

118

J86

2,597

D5

118_RX1_N

118

J86

2,597

B2

118_TX2_P

118

J86

2,787

B1

118_TX2_N

118

J86

2,789

B6

118_RX2_P

118

J86

2,681

B5

118_RX2_N

118

J86

2,680

A4

118_TX3_P

118

J86

3,044

A3

118_TX3_N

118

J86

3,044

A8

118_RX3_P

118

J86

3,515

A7

118_RX3_N

118

J86

3,515

Table 1-13:

GTX Transceiver Clock Inputs to the FPGA

U1 FPGA Pin

Net Name

Quad

Connector

R8

115_REFCLK0_P

115

J83

R7

115_REFCLK0_N

115

J83

U8

115_REFCLK1_P

115

J83

U7

115_REFCLK1_N

115

J83

L8

116_REFCLK0_P

116

J84

L7

116_REFCLK0_N

116

J84

N8

116_REFCLK1_P

116

J84

N7

116_REFCLK1_N

116

J84

G8

117_REFCLK0_P

117

J85

G7

117_REFCLK0_N

117

J85

J8

117_REFCLK1_P

117

J85

Table 1-12:

GTX Transceiver Pins

(Cont’d)

U1 FPGA Pin

Net Name

Quad

Connector

Trace Length

(mils)