16

KC724 GTX Transceiver Characterization Board

UG932 (v2.2) October 10, 2014

Chapter 1:

KC724 Board Features and Operation

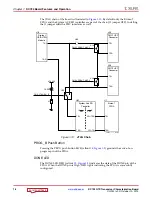

Active Heatsink Power Connector

An active heatsink (

) is provided for the FPGA. A 12V fan is affixed to the

heatsink and is powered from the 3-pin friction lock header J121 (

).

The fan power connections are detailed in

:

X-Ref Target - Figure 1-

8

Figure 1-8:

Active FPGA Heatsink

Table 1-4:

Fan Power Connections

Fan Wire

Header Pin

Black

J121.1 - GND

Red

J121.2 - 12V

Blue

J121.3 - NC

UG932_c1_08_062512