LISA-U1 series - System Integration Manual

3G.G2-HW-10002-3

Preliminary

System description

Page 21 of 125

output to

VCC

supply pins can mitigate the ripple on

VCC

, but adds extra voltage drop due to resistive

losses on series inductors

PWM mode operation

: select preferably regulators with Pulse Width Modulation (PWM) mode. While in

active mode Pulse Frequency Modulation (PFM) mode and PFM/PWM mode transitions must be avoided to

reduce the noise on the

VCC

voltage profile. Switching regulators able to switch between low ripple PWM

mode and high efficiency burst or PFM mode can be used, provided the mode transition occurs when the

GSM module changes status from idle mode (current consumption approximately 1 mA) to active mode

(current consumption approximately 100 mA): it is permissible to use a regulator that switches from the

PWM mode to the burst or PFM mode at an appropriate current threshold (e.g. 60 mA)

Output voltage slope

: the use of the soft start function provided by some voltage regulator must be

carefully evaluated, since the voltage at the

VCC

pins must ramp from 2.5 V to 3.2 V within 1 ms to allow a

proper switch-on of the module

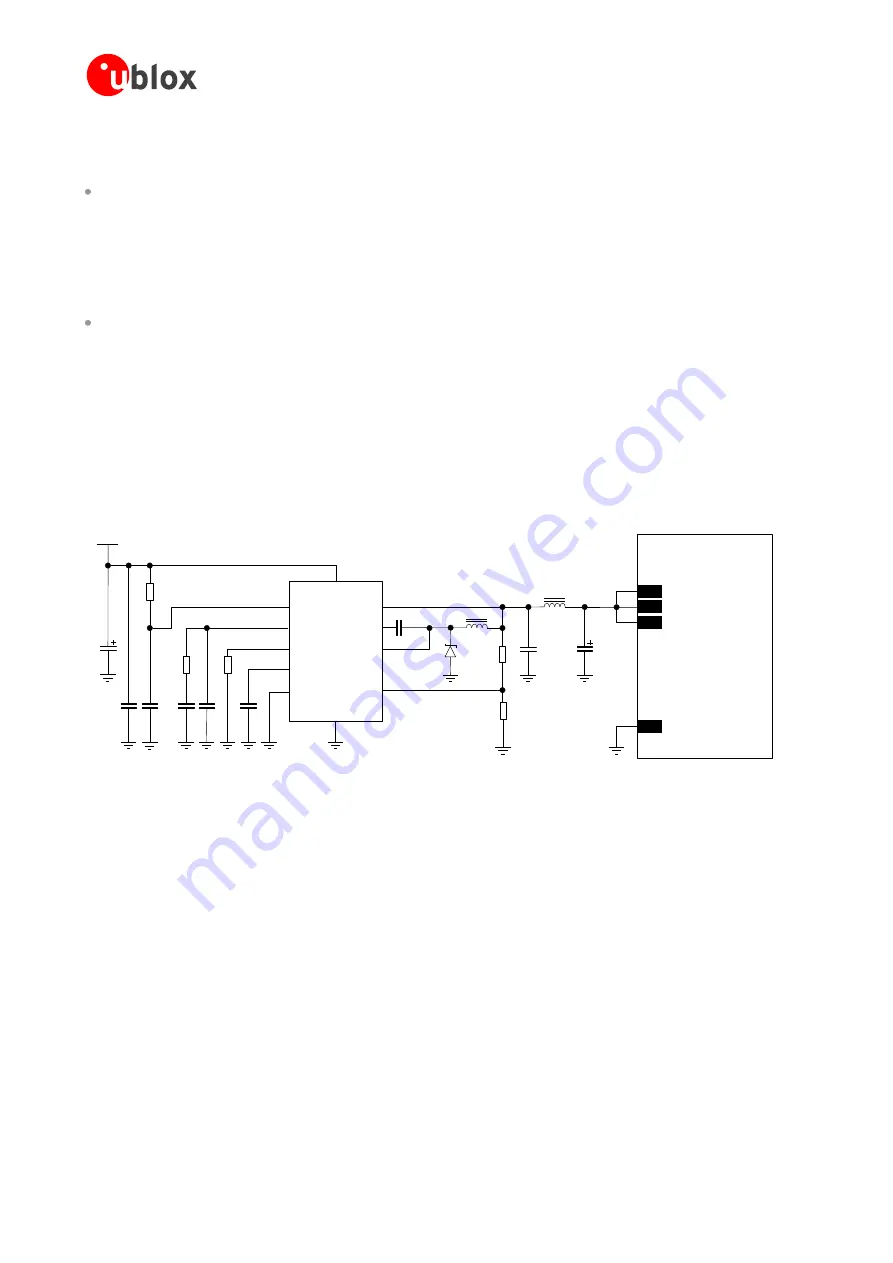

Figure 7 and the components listed in Table 5 show an example of a high reliability power supply circuit, where

the module

VCC

is supplied by a step-down switching regulator capable of delivering 2.5 A current pulses with

low output ripple and with fixed switching frequency in PWM mode operation greater than 1 MHz. The use of a

switching regulator is suggested when the difference from the available supply rail to the

VCC

value is high:

switching regulators provide good efficiency transforming a 12 V supply to the typical 3.8 V value of the

VCC

supply.

LISA-U1 series

12V

C6

R3

C5

R2

C3

C2

C1

R1

VIN

RUN

VC

RT

PG

SYNC

BD

BOOST

SW

FB

GND

6

7

10

9

5

C7

1

2

3

8

11

4

C8

C9

L2

D1

R4

R5

L1

C4

U1

62

VCC

63

VCC

61

VCC

GND

Figure 7: Suggested schematic design for the VCC voltage supply application circuit using a step-down regulator