SARA-G3 series - System Integration Manual

UBX-13000995 - R06

Objective Specification

Design-in

Page 108 of 218

2.2.1.2

Guidelines for PWR_ON layout design

The power-on circuit (

PWR_ON

) requires careful layout since it is the sensitive input available to switch

on the SARA-G3 modules until a valid

VCC

supply is provided after that the module has been switched

off by means of the AT+CPWROFF command: ensure that the voltage level is well defined during

operation and no transient noise is coupled on this line, otherwise the module might detect a spurious

power-on request.

2.2.2

Module reset (RESET_N)

2.2.2.1

Guidelines for RESET_N circuit design

, the module has an internal pull-up resistor on the reset input line:

an external pull-up is not required on the application board.

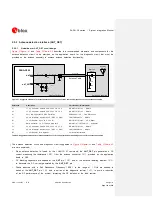

Connecting the

RESET_N

input to a push button that shorts the

RESET_N

pin to ground, the pin will be

externally accessible on the application device: according to EMC/ESD requirements of the application,

provide an additional ESD protection (e.g. EPCOS CA05P4S14THSG varistor array) on the line connected

to this pin, close to accessible point, as described in

ESD sensitivity rating of the

RESET_N

pin is 1 kV (Human Body Model according to JESD22-

A114). Higher protection level can be required if the line is externally accessible on the application

board, e.g. if an accessible push button is directly connected to

RESET_N

pin. Higher protection

level can be achieved by mounting an ESD protection (e.g. EPCOS CA05P4S14THSG varistor

array) close to accessible point.

Connecting the

RESET_N

input to an external device (e.g. application processor), an open drain output

can be directly connected without any external pull-up, as described in

: the internal pull-up resistor provided by the module pulls the line to the high logic level

when the

RESET_N

pin is not forced low by the application processor. A compatible push-pull output of

an application processor can be used too.

SARA-G3 series

18

RESET_N

Reset

push button

ESD

Open

Drain

Output

Application

Processor

SARA-G3 series

18

RESET_N

TP

TP

Figure 34: RESET_N application circuits using a push button and an open drain output of an application processor

Reference

Description

Remarks

ESD

Varistor for ESD protection

CT0402S14AHSG - EPCOS

Table 20: Example of ESD protection component for the RESET_N application circuit