Содержание TLCS-48 Series

Страница 1: ...TOSHIBA AMERICA INC ...

Страница 4: ......

Страница 5: ...INDEX PART 1 TLCS 48 Series PART 2 TLCS 90 Series APPENDIX TLCS 90 ...

Страница 6: ......

Страница 7: ...PART 1 TLCS 48 LSI DEVICES ...

Страница 8: ......

Страница 10: ......

Страница 194: ......

Страница 195: ...PART 2 TLCS 90 LSI DEVICES ...

Страница 196: ......

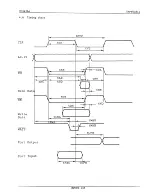

Страница 255: ...TOSHIBA H l rt CD Ii l o llJ rt llJ tI1 C Ul Reset Read Pl Fig 3 5 2 Port 1 MPU90 57 Port 1 P10 P17 TMP90C840 ...

Страница 339: ...APPENDIX TLCS 90 ...

Страница 340: ......

Страница 364: ......