B5

B6

B7

B4

B5

B6

B7

B3

B4

B5

B6

B7

D(R/X)

data delay 2

data delay 1

D(R/X)

data delay 0

D(R/X)

FS(R/X)

CLK(R/X)

0-bit period

2-bit period

1-bit period

B7

B6

B5

2 Bit Periods

Framing Bit

CLKR

FSR

DR

Preliminary

www.ti.com

Architecture

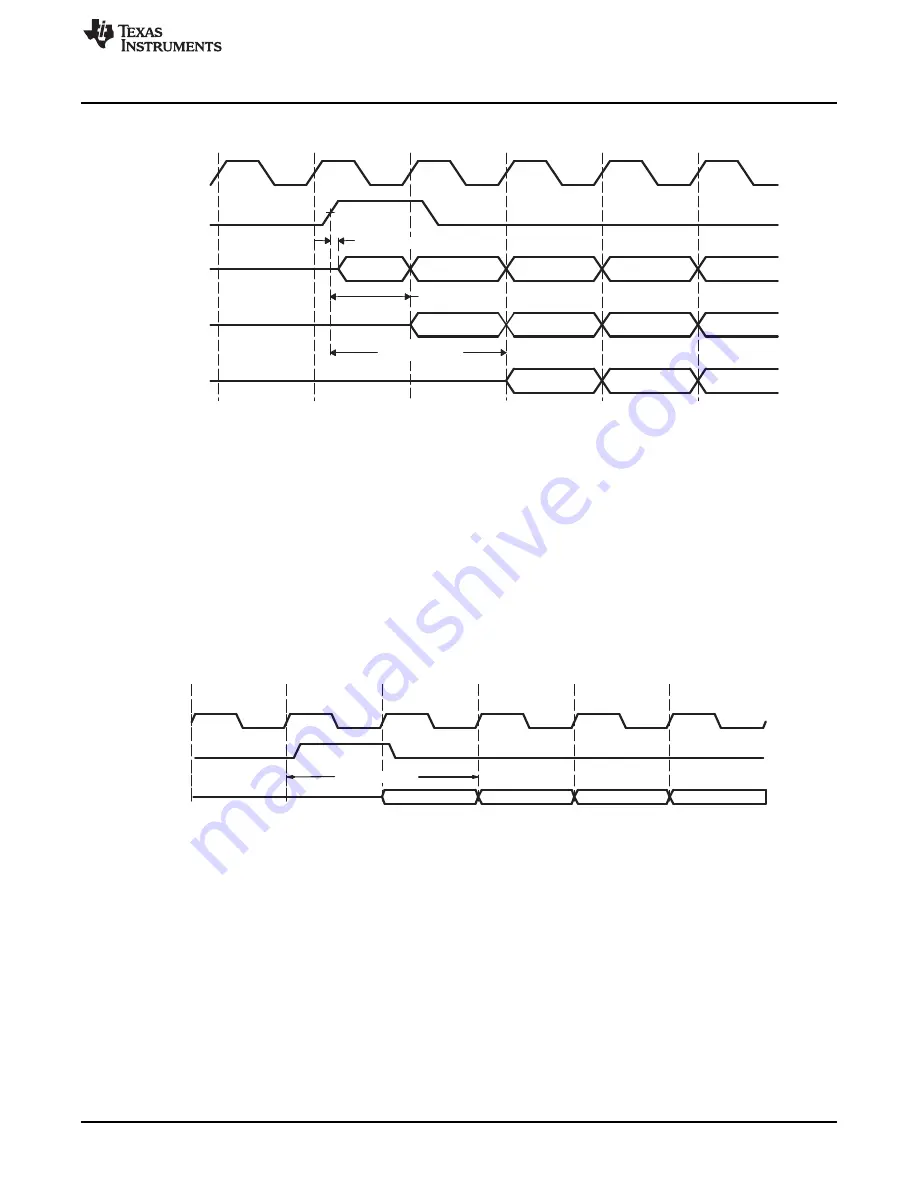

Figure 11-30. Range of Programmable Data Delay

0-bit data delay:

Normally, a frame–synchronization pulse is detected or sampled with respect to an edge of internal

serial clock CLK(R/X). Thus, on the following cycle or later (depending on the data delay value), data

may be received or transmitted. However, in the case of 0–bit data delay, the data must be ready for

reception and/or transmission on the same serial clock cycle.

For reception, this problem is solved because receive data is sampled on the first falling edge of CLKR

where an active–high internal FSR is detected. However, data transmission must begin on the rising

edge of the internal CLKX clock that generated the frame synchronization. Therefore, the first data bit is

assumed to be present in XSR1, and thus on McBSP.DX. The transmitter then asynchronously detects

the frame–synchronization signal (FSX) going active high and immediately starts driving the first bit to

be transmitted on the McBSP.DX pin.

Figure 11-31. 2-Bit Data Delay Used to Skip a Framing Bit

11.2.8.6.11 Set the Transmit DXENA Mode

DXENA bit (SPRC1_REG[7]) is used to set the transmit DXENA (DX delay enable) mode.

The DXENA bit controls the delay enabler on the McBSP.DX pin. Set DXENA to enable an extra delay

for turn–on time. This bit does not control the data itself, so only the first bit is delayed (the delay is

given by a combinatorial delay buffer). The inserted delay: 7 ns, 14 ns (default), 20 ns or 28 ns can be

set using the DXENDLY bit field in XCCR_REG register. If you tie together the McBSP.DX pins of

multiple McBSPs, make sure DXENA = 1 to avoid having more than one McBSP transmitting on the

data line at one time.

11.2.8.6.12 Set the Transmit Interrupt Mode (legacy only)

The XINTM bit field (SPCRX_REG[5:4]) determines which event generates a transmit interrupt request

to the CPU.

1169

SPRUGX9 – 15 April 2011

Multichannel Buffered Serial Port (McBSP)

© 2011, Texas Instruments Incorporated

Содержание TMS320C6A816 Series

Страница 2: ...Preliminary 2 SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 92: ...92 Read This First SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1122: ...1122 Multichannel Audio Serial Port McASP SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1562: ...1562 Real Time Clock RTC SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1658: ...1658 Timers SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1750: ...1750 UART IrDA CIR Module SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1984: ...1984 Universal Serial Bus USB SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...