PCI Interface

1-5

ThunderLAN Overview

1.3.2

Byte Ordering

ThunderLAN follows the

PCI Local Bus Specification convention when trans-

ferring data on the PCI bus. The PCI bus data is transferred on the PAD[31::0]

lines. PAD31 is the most significant bit, and PAD0 is the least significant bit.

The 32 data lines are enough to transfer four bytes per data cycle. Byte 0 is

the LSbyte and byte 3 is the MSbyte. Byte 0 uses bits 0 – 7, byte 1 uses bits

8 – 15, byte 2 uses bits 16 – 23, byte 3 uses bits 24 – 31.

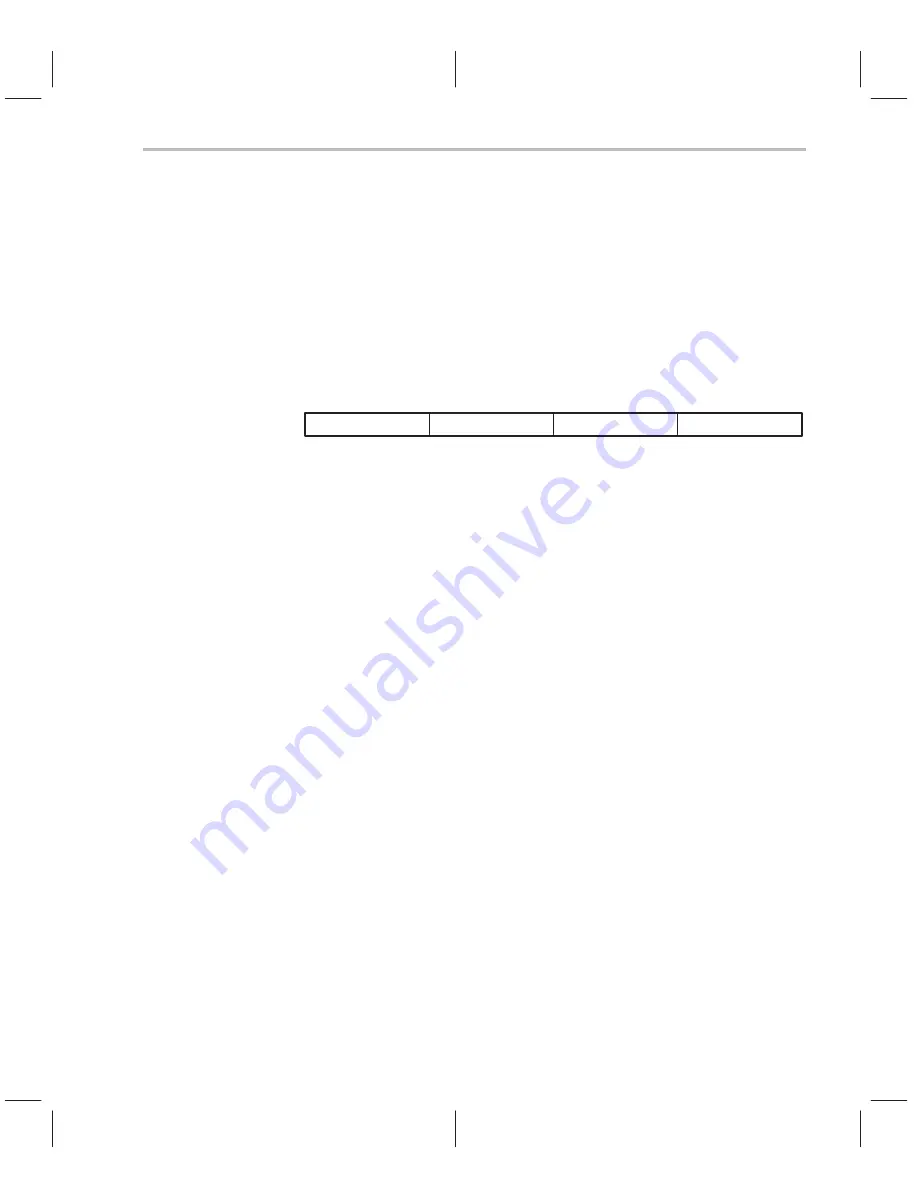

Figure 1–2. PCI Bus Byte Assignment

Byte 0

Byte 1

Byte 2

Byte 3

0

7

8

15

16

23

24

31

ThunderLAN uses the full four bytes per data cycle. The only exception is when

the data to be transferred is not octet aligned. In this case, the PCI controller

might not transfer the full four bytes on the first cycle. ThunderLAN deasserts

the IRDY signal only once, if needed, to synchronize the PCI bus to the internal

64-bit architecture. The deassertion of IRDY occurs on the third cycle of the

PCI bus. ThunderLAN does not deassert IRDY for the rest of the transfer un-

less the PCI bus asserts the TRDY signal.

Содержание ThunderLAN TNETE100A

Страница 1: ...ThunderLAN TNETE100A TNETE110A TNETE211 Programmer s Guide October 1996 Network Business Products ...

Страница 2: ...Printed in U S A October 1996 L411001 9761 revisionA SPWU013A ...

Страница 3: ......

Страница 17: ...xiv ...

Страница 23: ...1 6 ...

Страница 67: ...3 10 ...

Страница 81: ...4 14 ...

Страница 113: ...7 10 ...

Страница 165: ...A 52 ...

Страница 179: ...C 2 ...