Clock System Operation

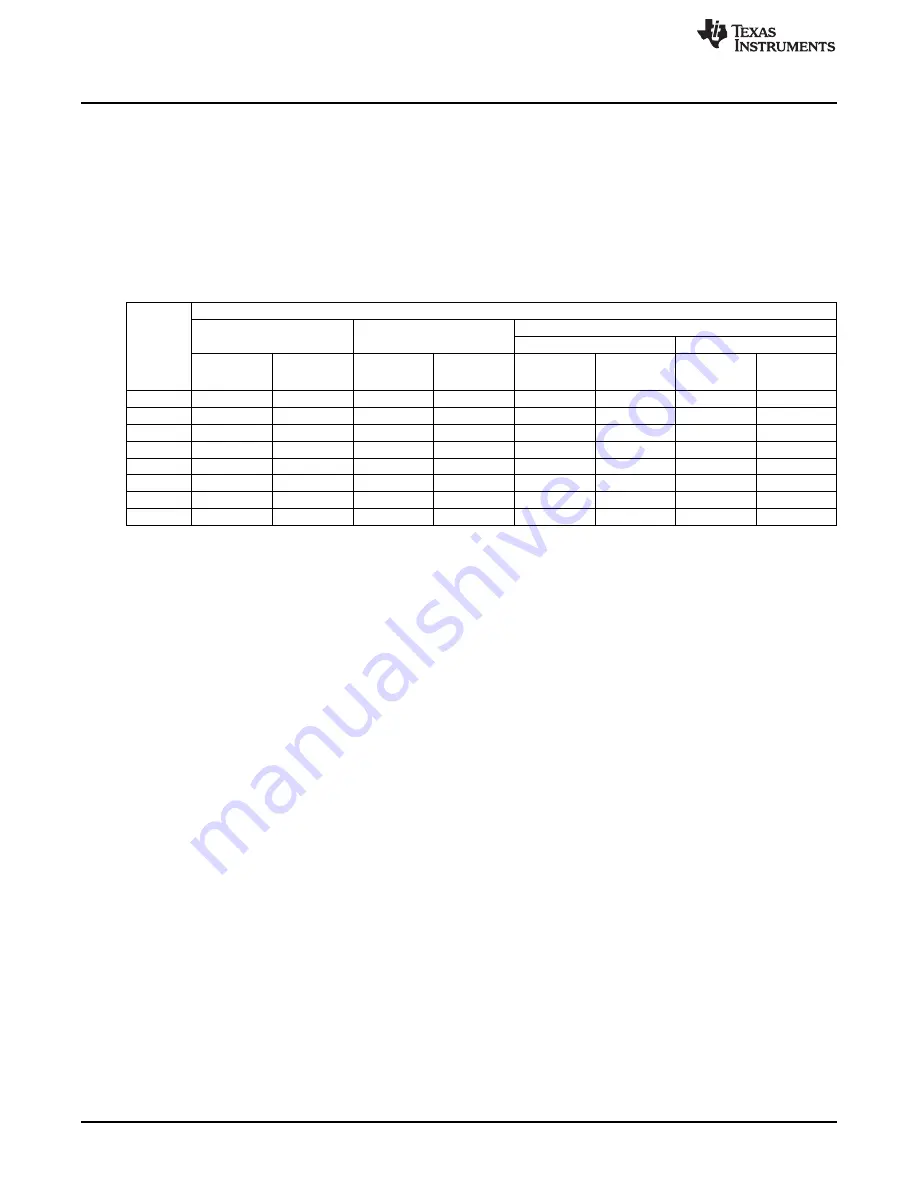

The function of the ACLKREQEN, MCLKREQEN, and SMCLKREQEN bits depends on which power mode

is selected; that is, they do not have an effect across all power modes. For example, ACLKREQEN

enables or disables ACLK requests. It is only effective in LPM4, because in all other modes (AM, LPM0,

LPM1, LPM2, LPM3), ACLK is always active. SMCLKREQEN enables or disables SMCLK requests.

When SMCLKOFF = 0 and in AM, LPM0, or LPM1, it is a don't care because SMCLK is always on in

these cases. For SMCLKOFF = 0 and in LPM2, LPM3, and LPM4, SMCLKREQEN can enable or disable

SMCLK requests, because in these modes, SMCLK is normally off. When SMCLKOFF = 1,

SMCLKREQEN can enable or disable SMCLK requests, because under this condition SMCLK is normally

off in all power modes. This is summarized in

Table 3-1. System Clocks vs Power Modes and Clock Requests

System Clocks

SMCLK

MCLK

ACLK

SMCLKOFF = 0

SMCLKOFF = 1

MCLKREQEN =

MCLKREQEN =

ACLKREQEN = 0

ACLKREQEN = 1

SMCLKREQEN =

SMCLKREQEN =

SMCLKREQEN =

SMCLKREQEN =

Mode

0 and clock

1 and clock

and clock

and clock

0 and clock

1 and clock

0 and clock

1 and clock

requested

requested

requested

requested

requested

requested

requested

requested

AM

Active

Active

Active

Active

Active

Active

Disabled

Active

LPM0

Disabled

Active

Active

Active

Active

Active

Disabled

Active

LPM1

Disabled

Active

Active

Active

Active

Active

Disabled

Active

LPM2

Disabled

Active

Active

Active

Disabled

Active

Disabled

Active

LPM3

Disabled

Active

Active

Active

Disabled

Active

Disabled

Active

LPM4

Disabled

Active

Disabled

Active

Disabled

Active

Disabled

Active

LPM3.5

Disabled

Disabled

Disabled

(1)

Disabled

Disabled

Disabled

Disabled

Disabled

LPM4.5

Disabled

Disabled

Disabled

Disabled

Disabled

Disabled

Disabled

Disabled

(1)

LFXTCLK is available directly as the clock source to the RTC module.

3.2.7 CS Module Fail-Safe Operation

The CS module incorporates an oscillator-fault fail-safe feature. This feature detects an oscillator fault for

XT1 and XT2 as shown in

. The available fault conditions are:

•

Low-frequency oscillator fault (XT1OFFG) for XT1 in LF mode

•

High-frequency oscillator fault (XT1OFFG) for XT1 in HF mode

•

High-frequency oscillator fault (XT2OFFG) for XT2

•

External clock signal faults for all bypass modes; that is, XT1BYPASS = 1 or XT2BYPASS = 1

The crystal oscillator fault bits XT1OFFG and XT2OFFG are set if the corresponding crystal oscillator is

turned on and not operating properly. Once set, the fault bits remain set until reset in software, even if the

fault condition no longer exists. If the user clears the fault bits and the fault condition still exists, the fault

bits are automatically set again, otherwise they remain cleared.

The OFIFG oscillator-fault interrupt flag is set and latched at POR or when any oscillator fault (XT1OFFG

or XT2OFFG) is detected. When OFIFG is set and OFIE is set, the OFIFG requests a user NMI. When the

interrupt is granted, the OFIE is not reset automatically as it is in previous MSP430 families. It is no longer

required to reset the OFIE. NMI entry and exit circuitry removes this requirement. The OFIFG flag must be

cleared by software. The source of the fault can be identified by checking the individual fault bits.

If XT1 in LF mode is sourcing any system clock (ACLK, MCLK, or SMCLK), and a fault is detected, the

system clock is automatically switched to the VLO for its clock source (VLOCLK). Similarly, if XT1 in HF

mode is sourcing any system clock and a fault is detected, the system clock is automatically switched to

MODOSC for its clock source (MODCLK). When XT2 (if available) is sourcing any system clock and a

fault is detected, the system clock is automatically switched to MODOSC for its clock source (MODCLK).

The fail-safe logic does not change the respective SELA, SELM, and SELS bit settings. The fail-safe

mechanism behaves the same in normal and bypass modes.

76

Clock System (CS)

SLAU272C – May 2011 – Revised November 2013

Copyright © 2011–2013, Texas Instruments Incorporated