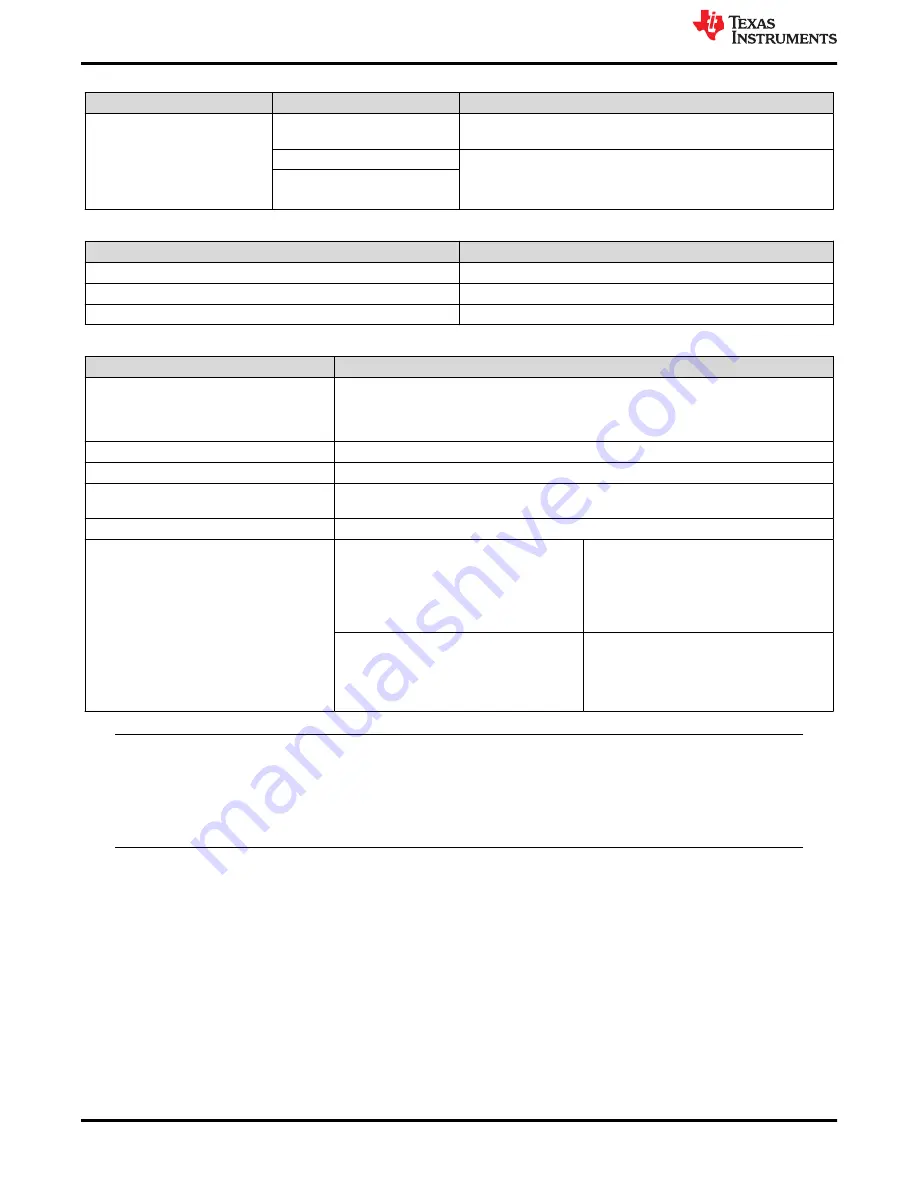

Table 3-3. Header J18 Description (continued)

Option Pins

Configuration

Description

GPIO2, TRIG_WDG, GPIO4

Open (Default)

GPIO mode. GPIO7 of the PMIC is connected to PH0 of the through

a level translator.

GPIO2, TRIG_WDG Closed

Trigger signal for trigger mode watchdog. VIO Select must be 3.3 V.

GPIO7 or GPIO6 supports the trigger mode watchdog signal when

the PMIC is in the Alternative function.

TRIG_WDG, GPIO4 Closed

Table 3-4. Header J33 VIO Voltage Select

Configuration

Description

Open

Not Allowed

VIO Select, 3.3 V: Closed (Default)

VIO is 3.3 V.

VIO Select, 1.8 V: Closed

VIO is 1.8 V.

Table 3-5. Header J24, 3.3V/5V, GPIO2/I2C/SPI

Configuration

Description

3.3V, VCCA: Closed

3.3 V from TLV733P-Q1 (U12) is connected to VCCA. The input for U12 is the 5 V from the

USB connection (VBUS). VBUS is not intended to support heavy load conditions. 2 W is the

maximum power which can be drawn from the USB. This header configuration is the normal

state of EVM.

EN_5V0, 3.3V, VCCA,5.0V: Open

VBUS, and USB_3V3 are isolated. VCCA is powered from J7.

EN_5V0,3.3V: Closed

5V from USB port is enabled. 5V regulated supply can be used to power up VCCA.

VCCA, 5.0V: Closed

5 V from USB Port is connected to VCCA. This supply is not intended to support heavy load

conditions Do not draw more than 2 W from the USB.

SCL2/CS, GPIO2: Open

GPIO mode. GPIO2 of the PMIC is connected to IO2 of the MCU.

SCL2/CS, GPIO2: Closed (Default)

I

2

C mode (J18 SPI_EN: Open)

Q&A Watchdog mode. GPIO2 and GPIO3

supports the Q&A Watchdog when the

PMIC is in Alternative function and the I

2

C

mode selected. This setting is also done

on connector J18 by closing GPIO3 to

SDA2/SDO if I2C2 is wanted to be used.

SPI mode (J18 SPI_EN: Closed)

SPI mode, Chip Select. GPIO2 and GPIO3

supports SPI communication when the PMIC

is in the Alternative function. This setting

is also done on connector J18 by closing

GPIO3 to SDA2/SDO.

Note

The PMIC device can be configured for a power good level of 3.3 V or 5.0 V for the VCCA pin.

If VCCA_VMON feature is enabled please check that the input voltage is correct and use sense

connection to compensate IR voltage drop with heavy load currents. Align the 3.3V/5.0V jumper with

the PMIC configuration. The default PMIC configuration supports the whole recommended VCCA

voltage range.

3.4 Connectors

Four SMA (J3, J5, J6, J16) connectors are included in the EVM, one for each buck. These connectors can be

used for noise and ripple measurements and are DC filtered with 10 µF capacitors and terminated with 50 Ω

resistors. The location of the DC filtering capacitor can be changed to alter the measurement point to be either

after or before the second LC filtering stage. The default configuration is that each of the connectors take the

measurement after the filter. The corresponding DC capacitor footprints are marked on the bottom side of the

PCB as shown in

EVM Details

6

LP876242-Q1 Evaluation Module

SLVUC20A – MARCH 2021 – REVISED AUGUST 2022

Copyright © 2022 Texas Instruments Incorporated