Signal Connections and Test Point Descriptions

5

SNVU518 – April 2016

Copyright © 2016, Texas Instruments Incorporated

LM5175RHF (QFN) EVM User Guide

3

Signal Connections and Test Point Descriptions

3.1

Test Point Descriptions

Table 2. Test Point Descriptions

LABEL

DESCRIPTION

VIN

Input voltage positive power and sense connection

GND

Input voltage negative power and sense connection

VOUT

Output voltage positive power and sense connection

GND

Output voltage negative power and sense connection

AGND

Analog GND

SYNC

External frequency synchronization input (SYNC). This terminal is connected to

the RT/SYNC pin of the LM5175 controller through a 100 pF capacitor on the

board.

EN

ENABLE input; tie to GND to disable converter

PGOOD

Power Good output

3.2

Optional Configurations

Table 3. Optional Configurations

COMPONENT

DESCRIPTION

R8

R8 can be used to select DCM or CCM mode and for enabling hiccup mode current

limit. See LM5175 device datasheet for R8 values. Default EVM configuration is

CCM/No hiccup.

Rcd

Dither is disabled by default. Replace with an appropriate capacitor to enable dither.

See LM5175 datasheet on how to set the dither frequency.

3.3

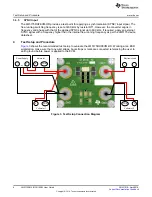

Signal Connections

3.3.1

Input Voltage Monitoring

The LM5175RHFEVM-HD provides two solder lug test points for measuring input voltage at the input

banana connections. This allows the user to measure the actual input voltage without losses from input

cables and connectors. All input voltage measurements should be made between VIN and GND test

points.

3.3.2

Output Voltage Monitoring

The LM5175RHFEVM-HD provides two solder lug test points for measuring output voltage at the output

banana connections. This facilitates measurement of the output voltage without losses related to output

cables and connectors.

3.3.3

Power Good Voltage Output

The LM5175RHFEVM-HD provides a test point for measuring the PGOOD flag voltage. A 20-k

Ω

pullup

resistor, Rpg, to VCC is included. For true open-drain operation with no pullup, remove Rpg. One possible

scenario where a PGOOD pullup is not required involves PGOOD of an upstream converter connected to

the EN input of a downstream converter to provide sequential startup of multiple regulators.

3.3.4

Enable Voltage Input

The LM5175RHFEVM-HD provides a test point for measuring the EN voltage. Shorting this test point to

GND disables the converter. The EN/UVLO voltage should not exceed the input voltage.