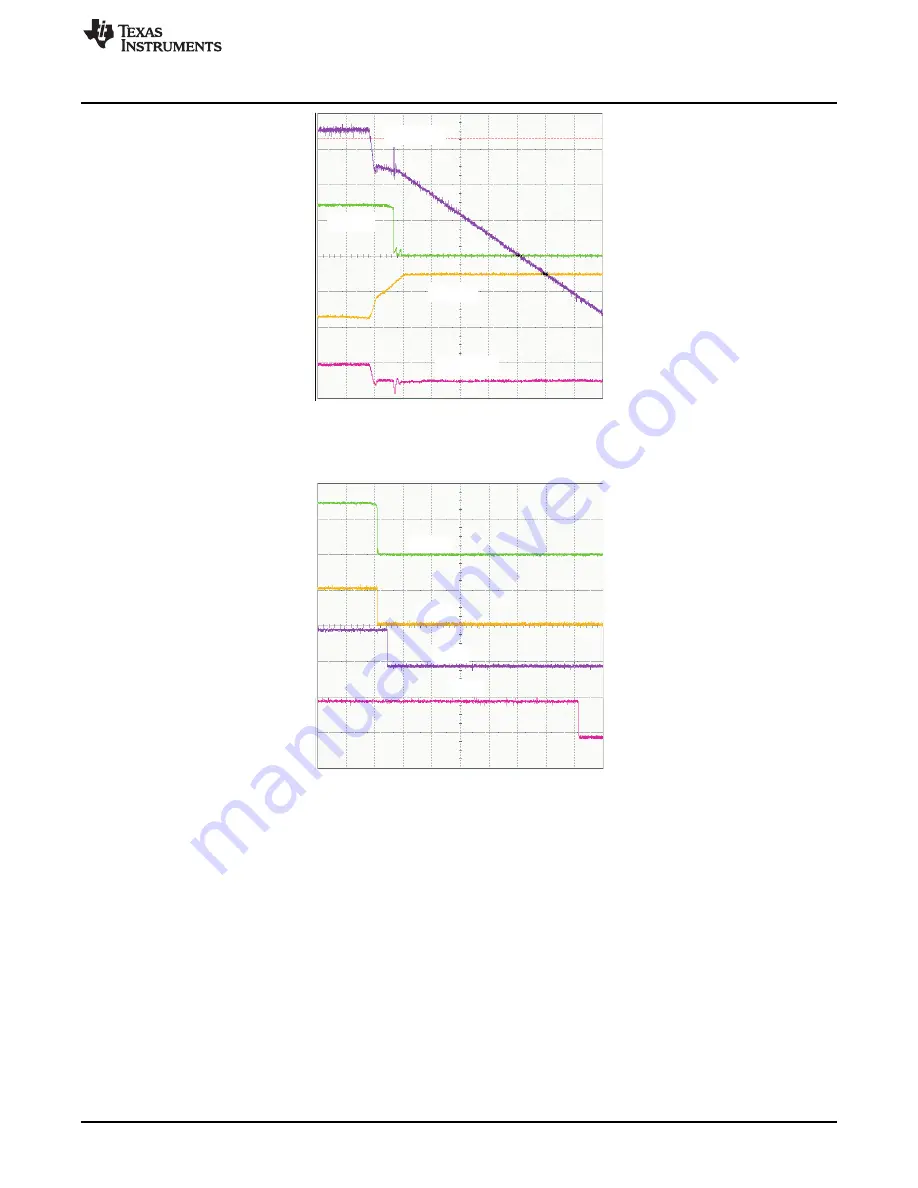

GATE1 - 10 V/div

FAULT - 5 V/div

STAT - 5 V/div

PG - 5 V/div

PSI - 100 mV/div

GATE2 - 10 V/div

GATE1 - 10 V/div

LOAD - 200 mV/div

Scope Traces

9

SLVU181B – October 2006 – Revised September 2019

Copyright © 2006–2019, Texas Instruments Incorporated

TPS2410 EVM (HPA204)

Figure 5. PSI Set to Standby

Figure 6. PSI Set to Standby