6 ADS8555EVM Operation

This section provides step-by-step instructions for connecting the ADS8555EVM to the computer and evaluating

the performance of the ADS8555.

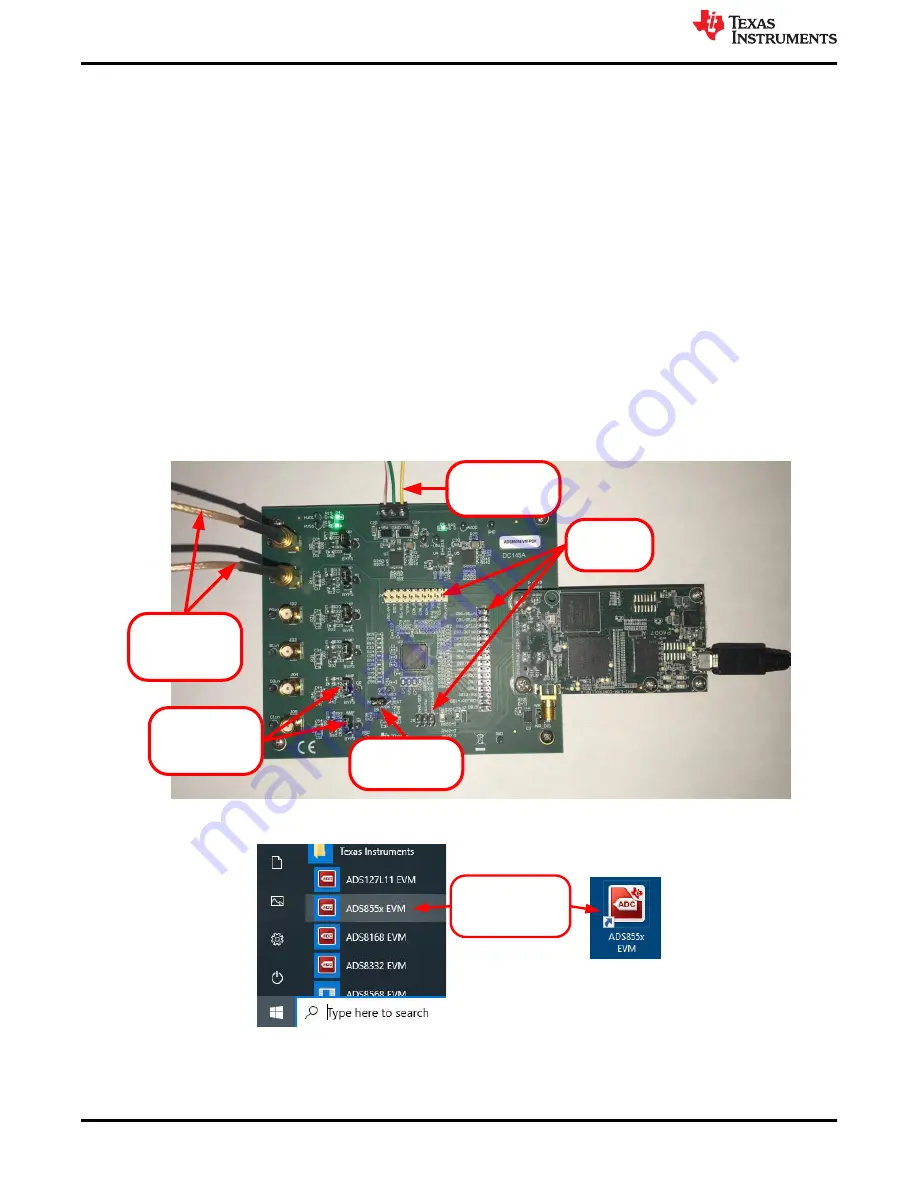

6.1 Connecting the Hardware and Running the GUI

1. Set the jumpers according to

2. Physically connect P2 of the PHI to J10 of the ADS8555EVM. Install the screws to assure a robust

connection.

3. Connect the USB on the PHI to the computer first.

a. LED D5 on the PHI lights up, indicating that the PHI is powered up.

b. LEDs D1 and D2 on the PHI start blinking to indicate that the PHI is booted up and communicating with

shows the resulting LED indicators.

4. As shown in

, start the software GUI. Notice that the LEDs blink slowly when the FPGA firmware is

loaded on the PHI. This process takes a few seconds, afterwards the AVDD and DVDD power supplies turn

on.

5. Connect the external ±15-V power supplies and GND to J1. This connection generates the AVDD, HVDD,

and HVSS supplies (HVDD = 12 V, HVSS = –12 V, and AVDD = 5 V).

6. Connect the signal generator. The default input range is ±10 V (or 10 Vpk). A common input signal applied is

a sinusoidal 1-kHz, 9.9-Vpk signal with a 0-V offset. This signal is adjusted just below the full-scale range to

avoid clipping.

JP06

External/Internal

Vref configuration

JP00

t

JP05

Bypass amplifier

jumper

ADS8555EVM

PHI

Controler

Input signals

connected to first

two channels.

+15V, -15V, GND

External Supply

Test point

headers

Figure 6-1. ADS8555EVM Hardware Setup and LED Indicators

Select EVM GUI from

start menu, or

associated shortcut.

Figure 6-2. Launch the EVM GUI Software

ADS8555EVM Operation

12

ADS8555EVM-PDK Evaluation Module

SLAU298A – NOVEMBER 2009 – REVISED MAY 2021

Copyright © 2021 Texas Instruments Incorporated