www.ti.com

2.2.4

ADC Clock Input

2.2.5

ADC Digital Outputs

2.2.6

Surface-Mount Jumper Selections

2.3

Deserialization and the TSW1200

Circuit Description

Users should connect a filtered, low-phase-noise clock input to J12. A transformer, T5, provides the

conversion from a single-ended clock signal into a differential clock signal. When selecting the clock signal

level, users should account for the transformer having an impedance ratio of 4, with a voltage step-up

of 2.

The ADS64XX ADC outputs serialized data, a bit clock (DCLK), and a frame clock (FCLK). These signals

are brought to a high-density Samtec™ connector, J15. Users have three options in processing the ADC

data.

1. Customers can use the mating logic analyzer breakout board and capture the ADC data using a logic

analyzer. Users would be required to perform a software deserialization of the digital data before

conducting analysis. Contact the factory for a breakout board for your logic analyzer.

2. Customers can create their own digital interface card which directly interfaces to the ADC. In this case,

customers would design their mating digital interface board with the Samtec part number

QSH-060-01-F-D-A, which is the companion part number to the EVM connector.

3. In most cases, customers can use a hardware deserialization solution such as the TSW1200. The

TSW1200 features a powerful Xilinx™ Virtex 4 that comes preloaded with both 12-bit and 14-bit

deserialization routines. In addition, customers can use the FPGA to develop their own deserializer and

digital prototypes. The digital output of the TSW1200 easily plugs into logic analyzers or TI's own

digital capture and analysis solution, the TSW1100.

The EVM features surface-mount jumpers in cases where either the signal integrity is important or the

functions are not often used.

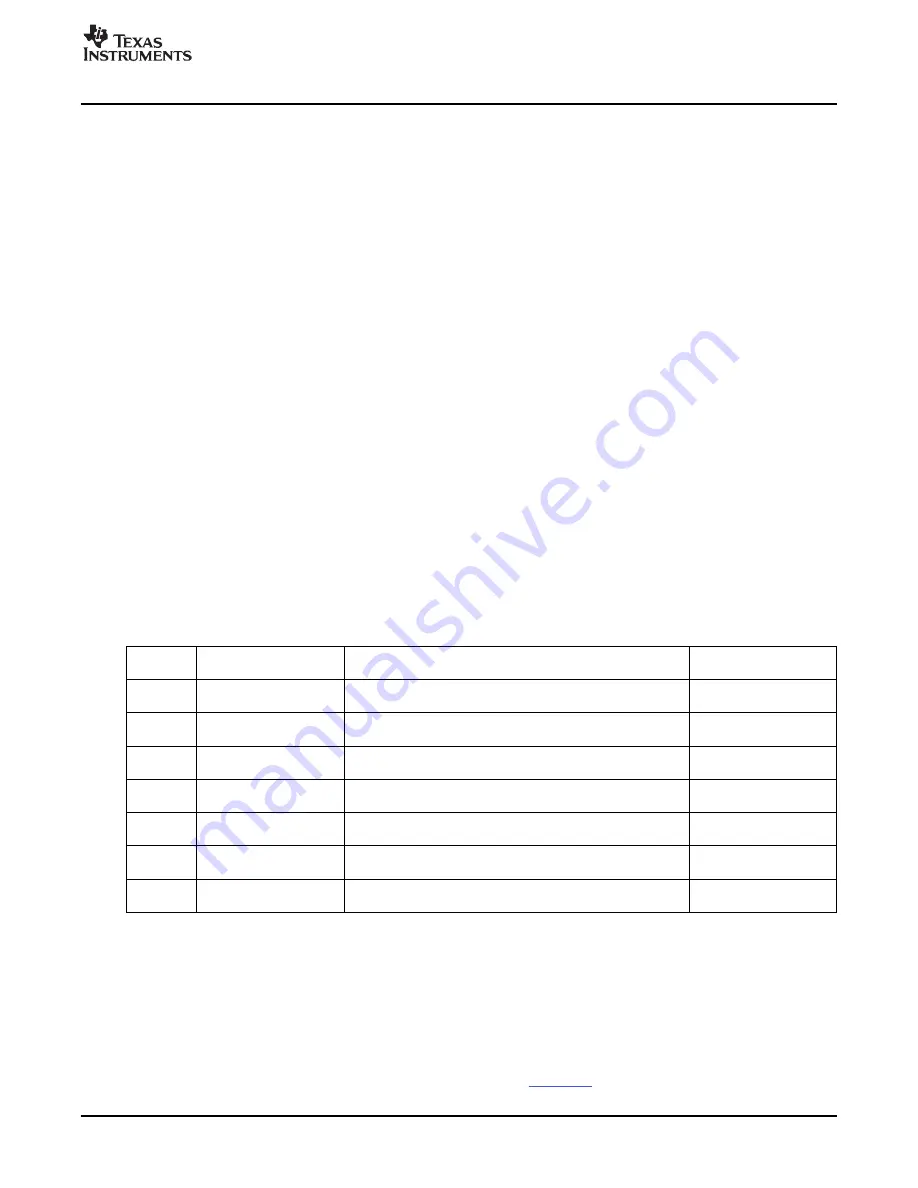

Table 2

summarizes these options.

Table 2. Surface Mount Jumpers

ADC

Reference Designator

Default Selection

Optional Selection

Signal

RESET

J7

2–3, parallel mode operation

1–2, serial mode

operation

SCLK

J6

Not populated, pin tied low

1–2, TSW1200 control

over SCLK

SDATA

J8

Not populated, pin tied low

1–2, TSW1200 control

over SDATA

SEN

J5

2–3: EVM J16 controls parallel operation modes

1–2, TSW1200 control

over SEN

PD

J9

Not populated, pin tied low, device operational

1–2, TSW1200 control

over PD

INC_M

JP1

2–3, Transformer-coupled analog input to channel C

1–2, Amplifier-coupled

path to channel C

INC_P

JP2

2–3, Transformer-coupled analog input to channel C

1–2, Amplifier-coupled

path to channel C

While the specifics of the deserializer are out of the scope of this user's guide, TI has partnered up with

Xilinx to deliver an open-source deserializer solution with application note documentation. When designing

the deserializer, users should consult Xilinx application note XAPP866, hosted on the Xilinx website. In

addition, TI has provided a guide to understanding the different digital output modes of the ADC and how

to pick the most appropriate digital output mode for deserialization. Users should consult

Demystifying the

Digital Output Choices of the ADS6XXX

, TI application note

SLAA348

.

SLAU196 – April 2007

9

Submit Documentation Feedback