73S1209F Data Sheet

DS_1209F_004

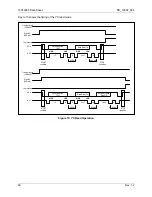

1.7.5 Timers and Counters

The 80515 has two 16-bit timer/counter registers: Timer 0 and Timer 1. These registers can be

configured for counter or timer operations.

In timer mode, the register is incremented every machine cycle, meaning that it counts up after every 12

periods of the MPU clock signal.

In counter mode, the register is incremented when the falling edge is observed at the corresponding input

signal T0 or T1 (T0 and T1 are the timer gating inputs derived from USR[0:7] pins, see the

section). Since it takes 2 machine cycles to recognize a 1-to-0 event, the maximum input count

rate is 1/2 of the oscillator frequency. There are no restrictions on the duty cycle, however to ensure

proper recognition of 0 or 1 state, an input should be stable for at least 1 machine cycle.

Four operating modes can be selected for Timer 0 and Timer 1. Two Special Function Registers (

) are used to select the appropriate mode.

The Timer 0 load registers are designated as TL0 and TH0 and the Timer 1 load registers are designated

as

Timer/Counter Mode Control Register (TMOD): 0x89

Å

0x00

Table 40: The TMOD Register

MSB LSB

GATE C/T M1 M0 GATE

C/T M1 M0

Timer 1

Timer 0

register start their associated timers when set.

Table 41: TMOD Register Bit Description

Bit Symbol

Function

TMOD.7

TMOD.3

Gate

If set, enables external gate control (USR pin(s) connected to T0 or T1

for Counter 0 or 1, respectively). When T0 or T1 is high, and TRx bit is

set (see the

register), a counter is incremented every falling edge

on T0 or T1 input pin. If not set, the TRx bit controls the corresponding

timer.

TMOD.6

TMOD.2

C/T

Selects Timer or Counter operation. When set to 1, the counter

operation is performed based on the falling edge of T0 or T1. When

cleared to 0, the corresponding register will function as a timer.

TMOD.5

TMOD.1

M1

Selects the mode for Timer/Counter 0 or Timer/Counter 1, as shown in

the

description.

TMOD.4

TMOD.0

M0

Selects the mode for Timer/Counter 0 or Timer/Counter 1, as shown in

the

description.

44

Rev.

1.2