MTLC User Manual

15

May 22, 2014

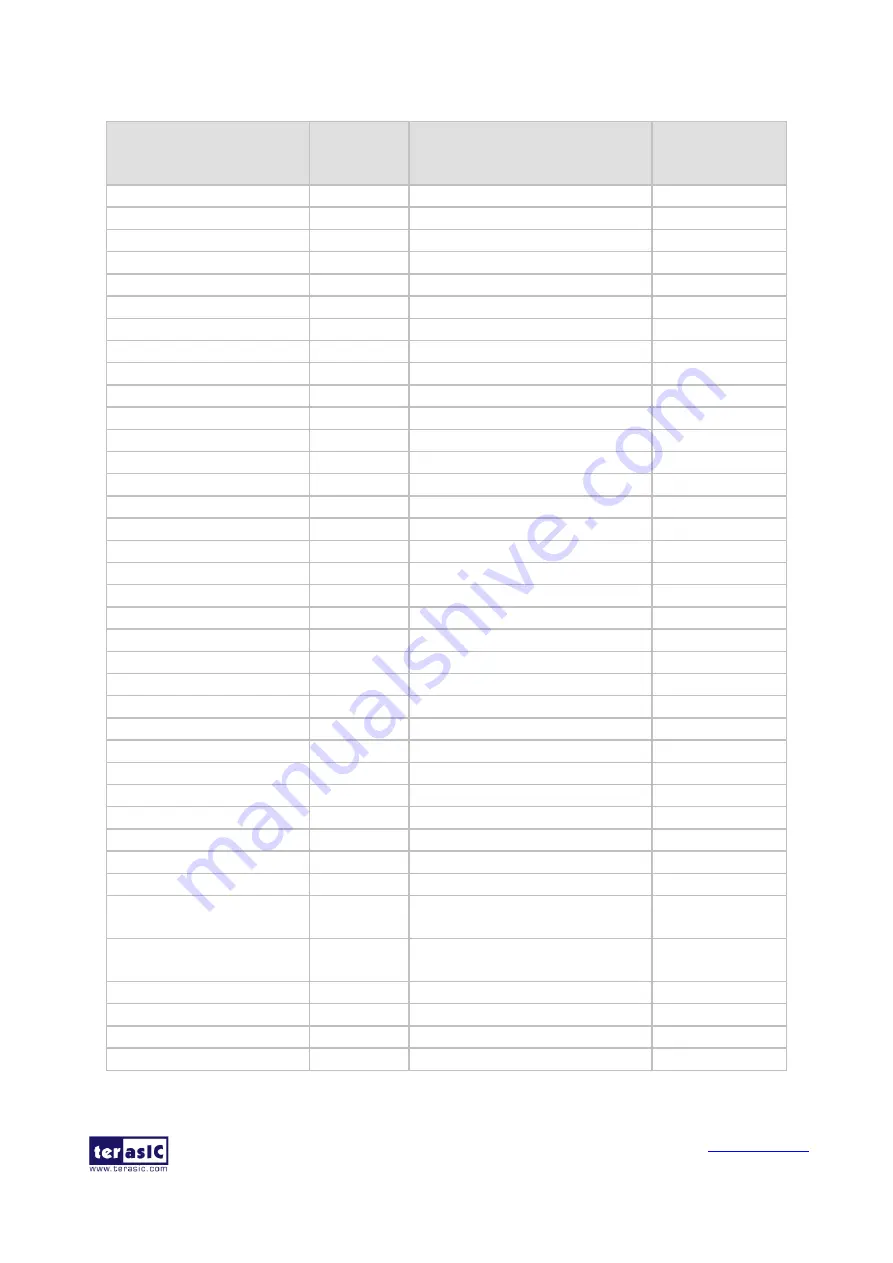

Table 3-2 Pin assignment of the LCD touch panel

Signal Name

FPGA

Pin

No.

Description

I/O

Standard

LCD_B0

P28

LCD blue data bus bit 0

2.5V

LCD_B1

P27

LCD blue data bus bit 1

2.5V

LCD_B2

J24

LCD blue data bus bit 2

2.5V

LCD_B3

J23

LCD blue data bus bit 3

2.5V

LCD_B4

T26

LCD blue data bus bit 4

2.5V

LCD_B5

T25

LCD blue data bus bit 5

2.5V

LCD_B6

R26

LCD blue data bus bit 6

2.5V

LCD_B7

R25

LCD blue data bus bit 7

2.5V

LCD_DCLK

V24

LCD Clock

2.5V

LCD_DE

H23

Data Enable signal

2.5V

LCD_DIM

P21

LCD backlight enable

2.5V

LCD_DITH

L23

Dithering setting

2.5V

LCD_G0

P26

LCD green data bus bit 0

2.5V

LCD_G1

P25

LCD green data bus bit 1

2.5V

LCD_G2

N26

LCD green data bus bit 2

2.5V

LCD_G3

N25

LCD green data bus bit 3

2.5V

LCD_G4

L22

LCD green data bus bit 4

2.5V

LCD_G5

L21

LCD green data bus bit 5

2.5V

LCD_G6

U26

LCD green data bus bit 6

2.5V

LCD_G7

U25

LCD green data bus bit 7

2.5V

LCD_HSD

U22

Horizontal sync input.

2.5V

LCD_MODE

L24

DE/SYNC mode select

2.5V

LCD_POWER_CTL

M25

LCD power control

2.5V

LCD_R0

V28

LCD red data bus bit 0

2.5V

LCD_R1

V27

LCD red data bus bit 1

2.5V

LCD_R2

U28

LCD red data bus bit 2

2.5V

LCD_R3

U27

LCD red data bus bit 3

2.5V

LCD_R4

R28

LCD red data bus bit 4

2.5V

LCD_R5

R27

LCD red data bus bit 5

2.5V

LCD_R6

V26

LCD red data bus bit 6

2.5V

LCD_R7

V25

LCD red data bus bit 7

2.5V

LCD_RSTB

K22

Global reset pin

2.5V

LCD_SHLR

H24

Left or Right Display

Control

2.5V

LCD_UPDN

K21

Up

/

Down

Display

Control

2.5V

LCD_VSD

V22

Vertical sync input.

2.5V

TOUCH _I2C_SCL

T22

touch I2C clock

2.5V

TOUCH _I2C_SDA

T21

touch I2C data

2.5V

TOUCH _INT_n

R23

touch interrupt

2.5V

Содержание MTLC

Страница 1: ...1 ...