2-10

X6DH8-G/X6DHE-G User's Manual

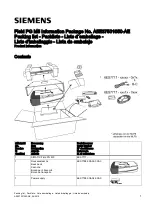

Power LED

The Power LED connection is lo-

cated on pins 15 and 16 of JF1.

Refer to the table on the right for

pin definitions.

NMI Button

The non-maskable interrupt button

header is located on pins 19 and

20 of JF1. Refer to the table on

the right for pin definitions.

Pin

Number

19

20

Definition

Control

Ground

NMI Button Pin

Definitions (JF1)

Pin

Number

15

16

Definition

Vcc

Control

PWR_LED Pin Definitions

(JF1)

Power Button

Overheat LED

1

NIC1 LED

Reset Button

2

Power Fail LED

HDD LED

Power LED

Reset

Pwr

Vcc

Vcc

Vcc

Vcc

Ground

Ground

19

20

Vcc

X

Ground

NMI

X

NIC2 LED

Vcc

GLAN1

®

J

L

A

N

1

S

UPER X6DH8-G

GLAN2

DIMM 2A (Bank 2)

DIMM 2B (Bank 2)

DIMM 3A (Bank 3)

DIMM 3B (Bank 3)

DIMM 4A (Bank 4)

DIMM 4B (Bank 4)

DIMM 1B (Bank 1)

DIMM 1A (Bank 1)

12V 8-pin

PWR

SMBus

PWR

J

F

1

FP Control

Fan2

JOH1

OH LED

C

H

I

n

tr

u

JL

1

WD

Enable

IPMI

ID

E

2

F

lop

py

COM2

BIOS

Ultra 320

SC

SI C

H

A

Ultra 320 SCSI CH B

Fan4

7902

CTRL

SATA0

SATA1

S

M

B

PCI-X100 MHz

PCI-X 100 MHz (ZCR)

PCI-X 3 133 MHz

Battery

J

P

L

1

RAGE-

X

PCI-E X8

Lindenhurst

North

Bridge

VGA

COM1

USB0/1

KB/

Mouse

Fan6 Fan5

ATX PWR

12V 4-Pin

PWR

Parrallel Port

J 3 8

24-Pin

F

a

n

7

J1D1

J1B1

JP10

J 1 2

Fan8

J 1 5

SCSI

CPU 0

CPU 1

JWOR1

SI/O

J 3 2

JP11

Alrm

Reset

3rd PS

Detect

PSF

Fan1

F

a

n

3

ID

E

1

WOR

JPA1

SCSI Enable

PCI-32 Bit 33 MHz

WOL

USB2/3

J

1

1

ICH

JD2

PW LED SPKR

JPG1

VGA

Enable

JWD

VGA

Slot1

Slot2

Slot3

Slot4

J

P

L

2

Slot5

Slot6

PCI-E X8

GLAN

CTLR

GLAN

CTLR

(Hance

Rapids)

J 6

J 5

inter. SPKR

PXH

JBT1

CL CMOS

J4F5

P

L

L

S

E

L

PS Fail

LED

JFP

Force PW On

J4F4

L

A

N

2

E

n

.

L

A

N

1

E

n

a

b

le

6300 ESB

E7520

NMI

PWR LED