STA309A

Registers

Doc ID 13855 Rev 4

39/67

7.2.32

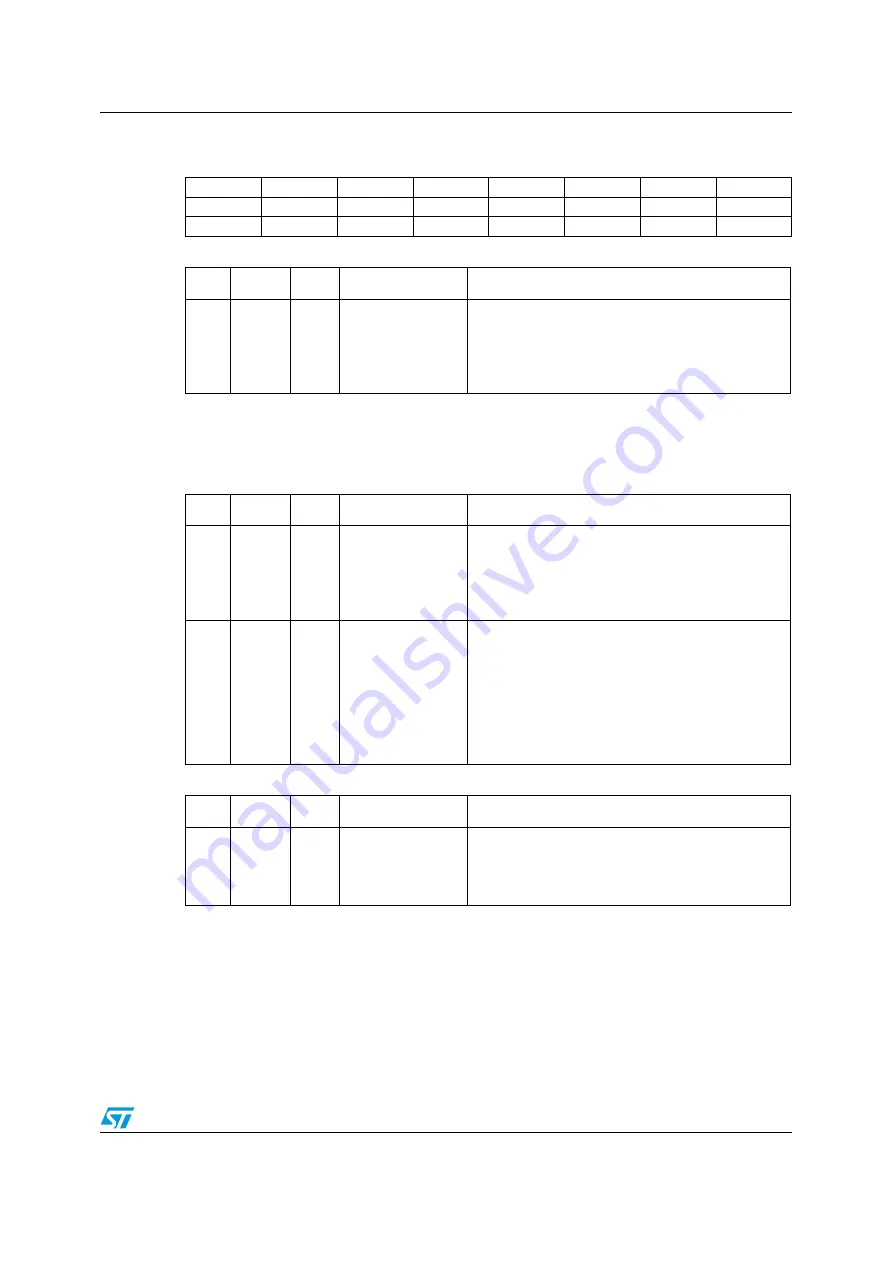

AUTO1 - Automode™ EQ, volume, GC (0x1F)

By setting AMEQ to any setting other than 00 enables Automode EQ, biquads 1-5 are not

user programmable. Any coefficient settings for these biquads will be ignored. Also when

Automode EQ is used the prescale value for channels 1-6 becomes hard-set to -18 dB.

Automode downmix setting uses channels 7-8 of Mix#1 engine and therefore these

channels of this function are fixed and not allowed to be user set when in this mode.

D7

D6

D5

D4

D3

D2

D1

D0

AMDM

AMGC2

AMGC1

AMGC0

AMV1

AMV0

AMEQ1

AMEQ0

0

0

0

0

0

0

0

0

Table 53.

AMEQ bits

Bit

RW

RST

Name

Description

1:0

RW

0

AMEQ[1:0]

Biquad 2-6 mode is:

00: user programmable

01: preset EQ - PEQ bits

10: graphic EQ - xGEQ bits

11: auto volume controlled loudness curve

Table 54.

AMV bits

Bit

RW

RST

Name

Description

3:2

RW

0

AMV[1:0]

Automode volume mode (MVOL) is:

00: MVOL 0.5 dB 256 steps (standard)

01: MVOL auto curve 30 steps

10: MVOL auto curve 40 steps

11: MVOL auto curve 50 steps

6:4

RW

0

AMGC[2:0]

Automode gain compression/limiters mode is:

000: user programmable GC

001: AC no clipping

010: AC limited clipping (10%), 90% signal unclipped

011: DRC nighttime listening mode

100: DRC TV commercial/channel AGC

101: AC 5.1 no clipping

110: AC 5.1 limited clipping (10%)

Table 55.

AMDM bit

Bit

RW

RST

Name

Description

7

RW

0

AMDM

Automode 5.1 downmix:

0: normal operation

1: channels 7-8 are 2-channel downmix of channels

1-6