SA-WSIS10/SS-IS10

10

10

SA-WSIS10/SS-IS10

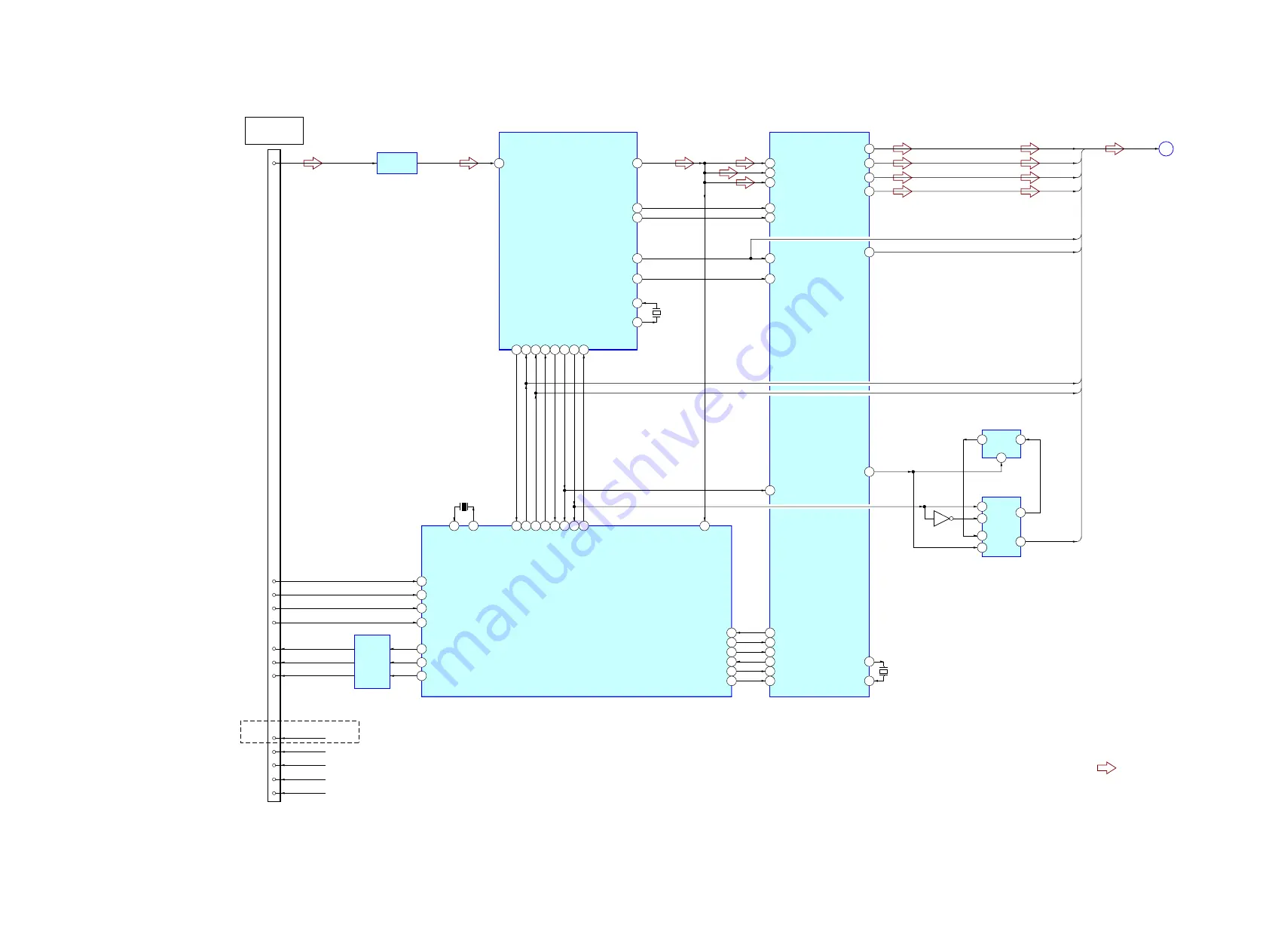

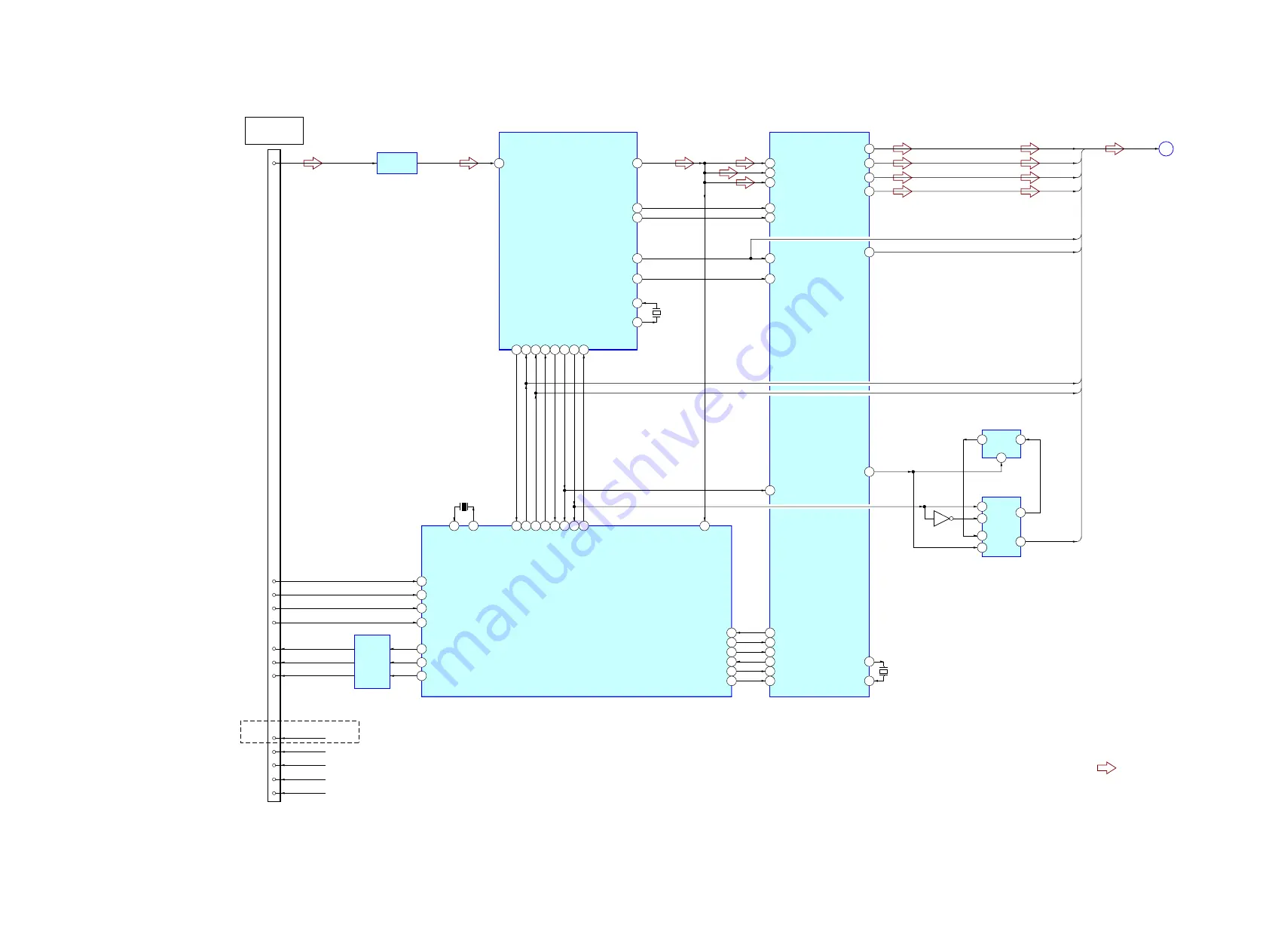

SECTION 4

DIAGRAMS

DIGITAL AUDIO INTERFACE RECEIVER

IC701

DSP

IC821

DO (O)

DIR_HDOUT

16

DATA (O)

24

AUDIO– (O)

14

BCK (O)

15

LRCK (O)

13

CKOUT (O)

3 DIN0 (I)

Xin

15

Xout

13

X610

10MHz

XIN (I) 22

XOUT (O) 21

X701

12.288MHz

35 36

100

DI (I)

DAMP_SCDT/DIR_DIN

1

CL (I)

DAMP_SHIFT/DIR_CLK

38

2

CE (I)

DIR_HCE

37

58

CSFLAG (O)

DIR_CSFLAG

25

19

ERROR (O)

DIR_ERROR

34

27

XSTATE (O)

DIR_XSTATE

17

60

DIR_ZERO

18

78 DPSIA

97 NOUAUDIO

∗

64

DPSOA

89 DPBCK

88 DPLRCK

94 DPFSCK

5

DSP_MOSI

16 DIR_ERR

127 MOSI

7

DSP_SPICLK

125 SPICLK

6

DSP_MISO

126 MISO

3

DSP_INT

15 INT_REQ

56

DSP_SPIDS

122 SPIDS

∗

55

DSP_RESET

121 RESET

∗

A

AMP BUS

DATA1

DATA2

65

DPSOB

DATA3

70

DPSOC

BCK

87

DPDVBCK

LRCK

MCK

86

DPDVLRCK

DATA4

71

DPSOD

XMODE (I)

DIR_RST

48

57

79 DPSIB

82 DPSIE

SCDT

SHIFT

SYSTEM CONTROLLER

IC611 (1/3)

• SIGNAL PATH

: AUDIO

5

6

SWITCHING

IC822

D FLIP-FLOP

IC820

3

4

1

2

D

2Y

CLK

Q

2B

2A

Q820

2

1

7

1Y

1A

1B

X820

25MHz

XTAL

CLKIN

143

142

LEVEL SHIFT

IC702

CN610

SYSTEM CONTROL

ONLY FOR

HCD-IS10

12

13

10

11

23

24

SYS_RXD

SYS_CLK

SYS_WAKEUP

SYS_TXD

SYS_BUSY

SYS_RESET

15

16

14

DM7V

A12V

UNREG-M9V

18

17

D7V

UNREG-D6V

DM +7V

(EXCEPT E32, AR)

A +12V

M +9V

D +7V

E +6V

25

CABLE_DETECT

20

SPDIF

SYS_TXD

31

SYS_BUSY

34

SYS_RESET

87

SYS_RXD

32

SYS_CLK

33

SYS_WAKEUP

74

CABLE DETECT

73

LEVEL

SHIFT

IC610

• Abbreviation

AR

: Argentina

E32

: Latin America models except Argentina

4-1. BLOCK DIAGRAM – DSP Section –

(Page 11)