– 10 –

ICX418AKL

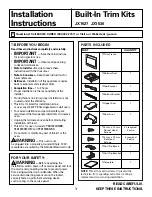

Clock Switching Characteristics

∗

1

When vertical transfer clock driver CXD1267AN is used.

∗

2

tf

≥

tr – 2ns.

∗

3

The overlap period for twh and twl of horizontal transfer clocks H

φ

1

and H

φ

2

is two.

Min.

two

Typ.

Max.

16

20

Unit

ns

Remarks

Item

Horizontal transfer clock

Symbol

H

φ

1

, H

φ

2

∗

3

Min.

twh

Typ. Max. Min. Typ. Max. Min. Typ. Max. Min. Typ. Max.

twl

tr

tf

2.3

11

1.5

2.5

20

5.38

13

1.8

20

5.38

51

15

0.01

0.01

3

19

0.5

0.5

15

15

0.01

0.01

3

250

19

0.5

Unit

µs

ns

ns

µs

ns

µs

Remarks

During readout

∗

1

∗

2

When draining

charge

Item

Readout clock

Vertical transfer

clock

Reset gate clock

Substrate clock

Symbol

V

T

V

φ

1

, V

φ

2

,

V

φ

3

, V

φ

4

H

φ

H

φ

1

H

φ

2

φ

RG

φ

SUB

Hor

iz

ontal

tr

ansf

er cloc

k

0.5

During

imaging

During

parallel-serial

conversion