HBD-TZ215/TZ715

HBD-TZ215/TZ715

23

23

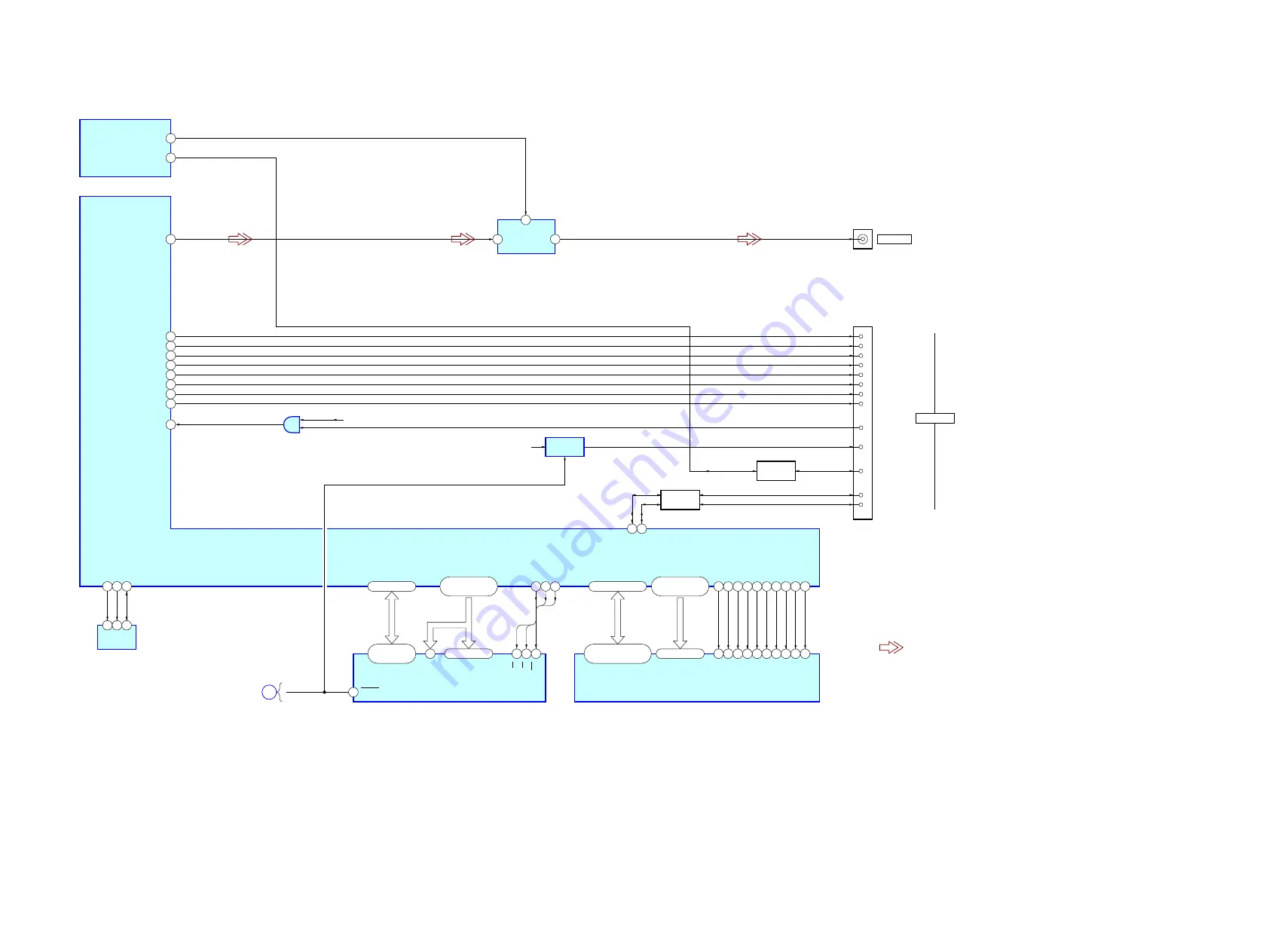

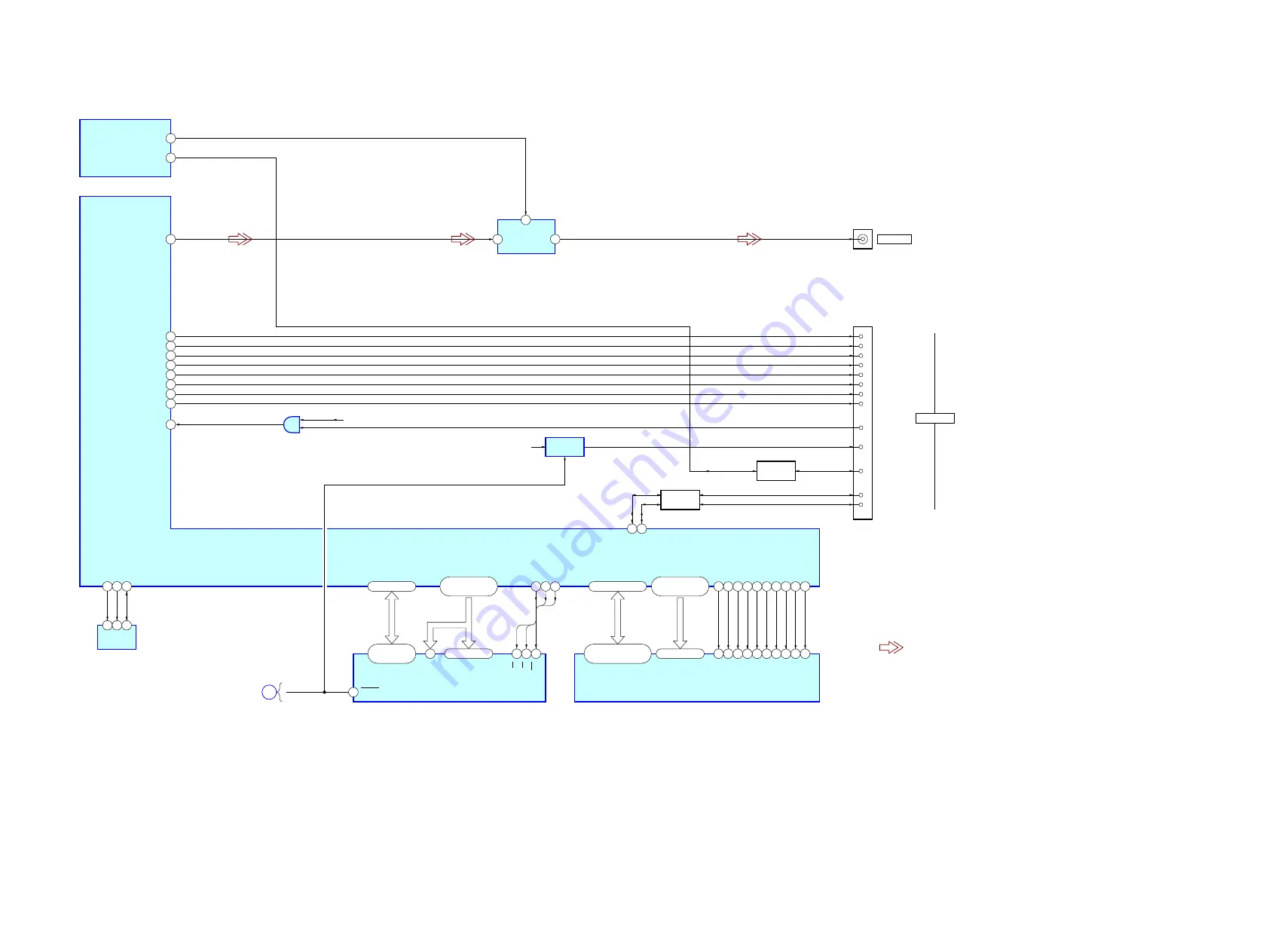

5-2. BLOCK DIAGRAM - VIDEO Section -

17

81

V_SEL0

CEC

D3.3V

1

2

4

CEC_TX_OUT

187

CVBS

180

TX2P

179

TX2N

177

TX1P

176

TX1N

174

TX0P

173

TX0N

171

TCKP

170

TCKN

162

HTPLG

VIDEO BUFFER

IC400

CN1701

CEC_TX_OUT

1 TMDS DATA2 +

3 TMDS DATA2 –

4 TMDS DATA1 +

6 TMDS DATA1 –

7 TMDS DATA0 +

9 TMDS DATA0 –

10 TMDS CLOCK +

12 TMDS CLOCK –

19 HPD

HDMI OUT

+6V

EEPROM

IC1103

BUFFER

IC1705

FLASH ROM

IC1102

DVD SYSTEM CONTROL, DSP

IC1101 (2/3)

SYSTEM CONTROL

IC503 (1/4)

SDRAM

IC1104

+5V REG.

IC1707

WE

EEWP

SCL

SDA

18 +5V POWER

13 CEC

15 SCL

16 SDA

7

112 101 102

DDC_CLK

161

DDC_DA

159

CLKE

37

UDQM

39

LDQM

15

WE

11

OE

28

CE

26

45

12

/CAS

17

/RAS

18

/WE

16

/CS

19

CLK

38

BA1

21

BA0

20

CKE

147

DQM1

132

DQM0

111

_CAS

134

_RAS

135

_R

WE

133

_RCS

136

DRCLK

146

BA1

138

BA0

137

XWR

66

XRD

78

XROMCS

XWR

XRD

XROMCS

A1–A21

A0

76

SCL

6

SDA

5

LEVEL SHIFT

Q1701

LEVEL SHIFT

Q9730

139–141,143,144

149–155

2,4,5,7,8,10,11,13,42,

44,45,47,48,50,51,53

117–113,119–129

22–26,29–35

RD0–RD15

RA0–RA11

RD0–RD15

RA0–RA11

56–64,67–75,77,

87,91,92

29,31,33,35,

38,40,42,44

79,80,82–86,89

25–16,10–1,48

HD0–HD7

HA0–HA21

A0–A21

HD0–HD7

HD0–HD7

DQ0–DQ7

A0–A19,N.C

DQ15/A-1

RESET

XSYSRST

D

J400(1/2)

VIDEO OUT

1

IN2

SW

4

OUT 2

x

SIGNAL PATH

: VIDEO

(Page 24)