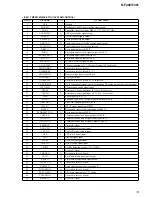

10

D-F200/F201

Pin No.

Pin Name

I/O

Pin Description

71

AM IN

I

AM oscillation signal input

72

VDD (1.8-2.2V)

—

Power supply pin

73

RESET

I

Power reset signal input

74

XOUT

O

Crystal oscillation signal output (75 kHz)

75

XIN

I

Crystal oscillation signal input (75 kHz)

76

VXT

—

Crystal oscillation signal pin

77

VLCD

—

LCD voltage doubler

78, 79

C1, 2

—

LCD voltage doubler

80

VEE

—

Constant voltage output to LCD.

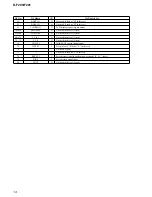

• IC601 CXD3029R (RF AMP, DIGITAL SIGNAL PROCESSOR, DIGITAL SERVO PROCESSOR, D-RAM CONTROLLER)

Pin No.

Pin Name

I/O

Pin Description

1

XRAS

O

Row address strobe signal output to the D-RAM (IC602)

2

XWE

O

Data input enable signal output to the D-RAM (IC602)

3 to 6

D1, D0, D3, D2

I/O

Two-way data bus with the D-RAM (IC602)

7, 8

TEST1, TEST2

O

Output terminal for the test Not used (open)

9

XCAS

O

Column address strobe signal output to the D-RAM (IC602)

10

WFCK

O

WFCK signal output terminal

11 to 13

A9 to A7

O

Address signal output to the D-RAM (IC602)

14

DVSS

—

Ground terminal (for D-RAM interface)

15 to 17

A6 to A4

O

Address signal output to the D-RAM (IC602)

18

XRDE

I

D-RAM read enable signal input terminal Not used (open)

19

VDD0

—

Power supply terminal (digital system)

20

CLOK

I

Serial data transfer clock signal input from the system controller (IC801)

21

SDTO

I

Serial data input from the system controller (IC801)

22

SENS

O

Serial data output to the system controller (IC801)

23

XLAT

I

Serial data latch pulse signal input from the system controller (IC801)

24

XSOE

I

Serial data output enable signal input from the system controller (IC801)

25

SYSM

I

Analog muting on/off control signal input from the system controller (IC801)

“H”: muting on

26

WDCK

O

GRSCOR signal output to the system controller (IC801)

27

SCOR

O

Subcode sync (S0+S1) detection signal output to the system controller (IC801)

28

XRST

I

Reset signal input from the system controller (IC801) “L”: reset

29

PWMI

I

Spindle motor external control signal input terminal (fixed at “L”)

30

XQOK

I

Subcode Q OK signal input terminal Not used (open)

31

XWRE

I

D-RAM write enable signal input terminal Not used (open)

32

R4M

O

System clock output to the system controller (IC801)

33

VSS0

—

Ground terminal (digital system)

34

SQCK

I

SQSO readout clock signal input terminal Not used (fixed at “H”)

35

SCLK

I

SENS serial data read clock signal input terminal Not used (fixed at “H”)

36

SQSO

O

CD text data output terminal Not used (open)

37

XEMP

O

D-RAM read prohibition signal output terminal Not used (open)

38

XWIH

O

D-RAM write prohibition signal output terminal Not used (open)

39

SBSO

O

Subcode P to W serial data output terminal Not used (open)

40

EXCK

O

SQSO readout clock signal output terminal Not used (pull down)

41

XSTL

I

Input terminal for the system clock frequency setting

“L”: 16.9344 MHz, “H”: 33.8688 MHz (fixed at “L” in this set)

42

HVSS

—

Ground terminal (for headphone)

43

HPL

O

PDM signal output for L-ch headphone to the headphone amplifier (IC302)

Not used (open)