- 14 -

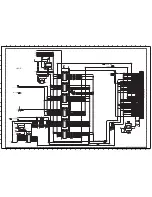

4-1. BLOCK DIAGRAM

Panel

L-SP

R-SP

Balancer

T-

CON

LVDS

H3E

H4

AC

IN

Top Key

Logo-LED

BASI

TAS

VERD

HDMI

EQ

UFE4

PHY

CI-Buff

RF

Ether

PCM-CIA

MS

USB

RGB1

RGB2

Comp1

A-Out

HP-Out

HDMI-A

IN

PC-A

IN

MAIN

AMP

DDR

DDR

HDMI1

HDMI2

HDMI3

DMP

Opt-Out

TEMP

Sens

NVM

IIC_EXTRA

IIC_TAS

IIC_RTC

RTC

IIC

NVM

SCART

SCART

Audio OUT

Sel out

Sel out

Video IN

PC IN

EMMA3SL

(MPEG/AVC Dec)

VCT-

Premium

(A/V SW,C-Dec

3D-Comb,ADC

NR,Histogram

HDMI Dec

Scaler)

V-SW

BASI

(Audio)

DDR

DDR

NAND

FLASH

Video IN

(Side)

BGE

Caye

nne-S

IP5 (40”)

LAN

H4

Logo-LED

TAS

VERD

HDMI

EQ

UFE4

PHY

CI-Buff

MAIN

AMP

DDR

TEMP

Sens

NVM

RTC

NVM

EMMA3SL

(MPEG/AVC Dec)

VCT-

Premium

(A/V SW,C-Dec

3D-Comb,ADC

NR,Histogram

HDMI Dec

Scaler)

V-SW

BASI

(Audio)

DDR

DDR

NAND

FLASH

Block Diagram (W4500 AEP/UK)

IP5 (40”)

IP5 ( 46”)

G5 +D4+D5 (52”)

Change point from

W4000(AEP)

Spring Model