SiT9514x GUI-UM Rev 1.04

Page 69 of 95

GUI User Manual

Clock Generators, Jitter Cleaners, and Network Synchronizers

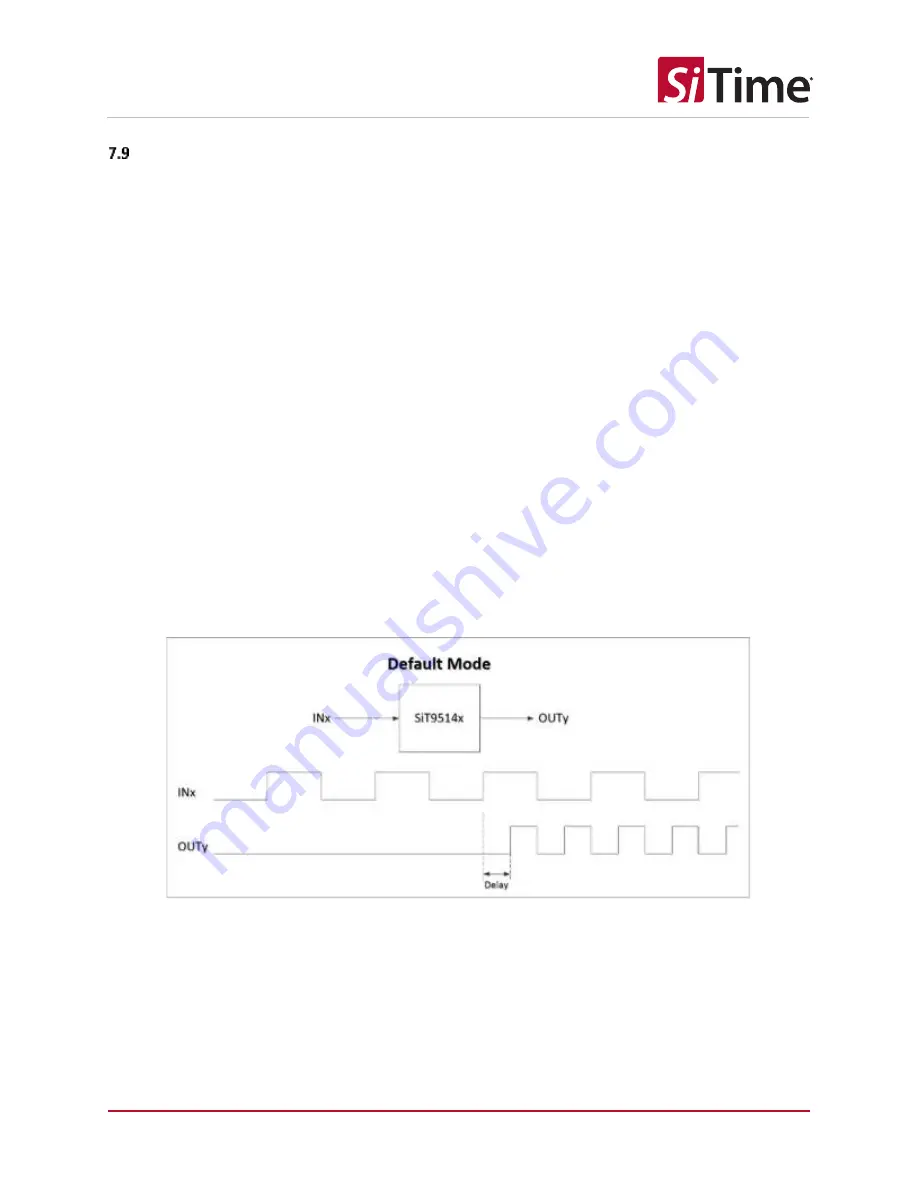

Input to output delay control feature

SiT9514x supports a unique transient performance feature for the output clock delay with respect to the

input clock. There exist two different operation modes:

•

Default mode of operation:

The output always starts with a fixed phase relationship to the input rising edge across multiple

power ups of the chip, see

o

The start of the output clock with respect to the rising edge of the input is the same

across multiple power ups with a total uncertainty of < ±175 ps.

o

The delay parameter shown above, is consistent across multiple power cycles, where:

Delay= A Fixed delay ± 175 ps

•

Input #3 Sync Mode of operation:

The output always starts with a fixed phase relationship to the rising edge of an independent

clock on Input #3 across multiple power ups of the chip, see

o

The start of the output clock with respect to the rising edge of Input #3 is the same

across multiple power ups of the device with a total uncertainty of < ±175 ps.

▪

Input #3

is an independent clock not related to the PLL input.

o

The delay parameter shown above, is consistent across multiple power cycles, where:

Delay = Fixed delay ± 175 ps

Figure 72: Input to output delay across multiple power ups in default mode