SAMSUNG Proprietary-Contents may change without notice

This Document can not be used without Samsung's authorization

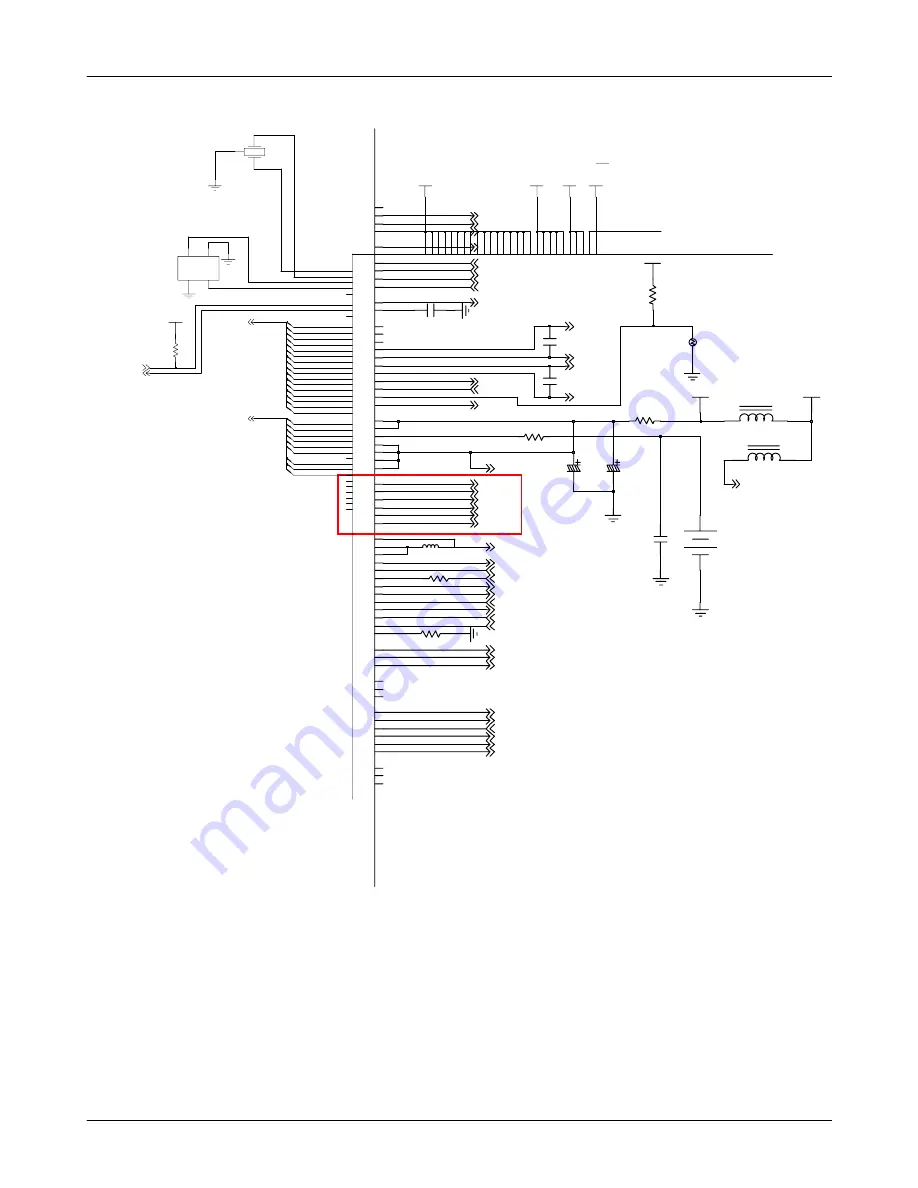

Flow Chart of Troubleshooting

9-2

C213

R203

TA202

TA201

VBAT_C_3.8V

BAT200

N

E

G

2

P

O

S

1

C211

C212

VANA_2.85V

VBAT

C216

W7

THERM_IN

W8

ACC_DET_IN

W9

ICHGP

W13

VCORE

SWCORE

W14

W15

PMU_VMEM

W16

PMU_VANA

W17

PMU_VGPIO

W18

EAR_OUT_P/L

W19

EAR_OUT_N/R

V9

PWM_OUT2

W10

GATE_REG

W12

ICHGN

HSET_OUT_P

V17

V18

HSET_OUT_N

V19

INTMIC_IN_P

V12

VCHG

V13

PMU_VRF

V14

SWCORE

V15

PMU_VSIM

U19

INTMIC_IN_N

U12

GND_VBAT_SNS

U13

VBAT_DCDC

U14

VBAT_DCDC

U15

PMU_VPERM

U17

VCM_OUT

T7

GATE_SW

T8

POK_OUT

T9

POK_IN

U10

PWM_OUT1

T14

VBAT_ANA

T15

VBAT_ANA

T19

EXTMIC_IN_P

R19

EXTMIC_IN_N

T10

VBAT_SENSE

T12

VBAT_ANA

T13

VBAT_ANA

P18

EXTMIC_BIAS

P19

HKSW_DET1

R18

INTMIC_BIAS

N18

AUXAUD_IN_L

N19

HKSW_DET2

AUXAUD_IN_R

M18

M19

AUX_ADC0

L19

PWM_OUT0

K18

PA_RAMP

J17

VBAT_RTC

FE_CTRL1

J18

H18

FE_CTRL0

G17

FE_CTRL3

G18

FE_CTRL2

F17

SIM_CLK

F18

SIM_RST

D9

DEBUG3

E19

SIM_DATA

TDI

D18

D10

C9

DEBUG4

C18

TMS

C19

TDO

B9

DEBUG5

B19

NTRST

A18

RTCK

A19

TCK

UCP200

TH200

R208

R204

L200

R202

L201

L202

R205

VBAT_ANA_3.8V

VBAT_AUDIO_3.8V

AUX_DET

RAMP

BAND_SEL

PON_PA

VMEM_1.8V

VGPIO_2.8V

ICHGN

CHG_REG

CHG_SW

ICHGP

RTCK

TMS

TCK

TDO

TRST_N

TDI

MOD_STANDBY

RCV_N

MIC_P

VCORE_1.25V

EAR_P

EAR_N

VF

VPERM_3.0V

VANA_2.85V

VRF_2.85V

VSIM_3.0V

EAR_MIC_N

VBAT

EAR_MIC_P

ONKEY_1

ONKEY_2

MIC_N

VCHG_P

RCV_P

SIM_DATA

SIM_CLK

SIM_RST

EAR_SW_REF

EAR_SW

MIC_BIAS

VCORE_1.25V

VSIM_3.0V

3

2

1

OSC200

VDEBUG_2.8V

W3

ADDR22

W5

ADDR13

W6

ADDR16

W2

NRESET_OUT

V6

ADDR9

V7

ADDR8

W1

ADDR14

W

1

1

V

D

D

_

V

P

E

R

M

V2

ADDR7

V3

ADDR21

V5

ADDR12

V1

ADDR18

ADDR6

U2

U3

DATA1

U4

DATA6

U6

ADDR10

U7

ADDR20

T

4

V

D

D

_

V

M

E

M

V

D

D

_

V

M

E

M

T

5

T

6

V

D

D

_

V

M

E

M

U1

ADDR11

T3

ADDR15

DATA9

R2

T1

DATA3

P2

ADDR17

P3

DATA14

N2

ADDR19

N3

DATA0

M3

DATA13

M

7

V

D

D

_

V

C

O

R

E

L

7

V

D

D

_

V

C

O

R

E

L

8

V

D

D

_

V

C

O

R

E

L

9

V

D

D

_

V

C

O

R

E

L

1

1

V

D

D

_

V

C

O

R

E

L

1

2

V

D

D

_

V

C

O

R

E

L

1

3

V

D

D

_

V

C

O

R

E

L2

DATA4

L3

DATA7

K19

CLK_XOUT

DATA5

K2

K3

DATA15

K

7

V

D

D

_

V

C

O

R

E

K

8

V

D

D

_

V

C

O

R

E

K

9

V

D

D

_

V

C

O

R

E

L

1

0

V

D

D

_

V

C

O

R

E

K1

DATA10

K

1

0

V

D

D

_

V

C

O

R

E

K

1

1

V

D

D

_

V

C

O

R

E

K

1

2

V

D

D

_

V

C

O

R

E

K

1

3

V

D

D

_

V

C

O

R

E

K

1

4

V

D

D

_

V

C

O

R

E

J19

XTAL_32K_1

J2

DATA2

J1

DATA8

J

1

4

V

D

D

_

V

C

O

R

E

H19

XTAL_32K_2

H2

DATA11

G

1

9

V

D

D

_

S

IM

H1

DATA12

E

1

7

V

D

D

_

V

G

P

IO

D

1

7

V

D

D

_

V

G

P

IO

D19

NRESET

D

1

1

V

D

D

_

V

G

P

IO

D

1

2

V

D

D

_

V

G

P

IO

D

1

6

V

D

D

_

V

G

P

IO

A

9

B13

TEST

A6

XTAL_26M_2

A7

XTAL_26M_1

UCP200

R

2

0

1

VBAT_ANA_3.8V

VMEM_1.8V

VGPIO_2.8V

VGPIO_2.8V

OSC201

2

GND1

GND2

4

HOT

1

3

HOT

A(13:22)

SYSRST

RSTON

A(15)

A(14)

A(13)

A(22)

MD(9)

MD(8)

MD(7)

MD(6)

MD(5)

MD(4)

MD(3)

MD(2)

MD(1)

MD(0)

A(21)

A(20)

A(19)

A(18)

A(17)

MD(15:0)

MD(15)

MD(14)

MD(13)

MD(12)

MD(11)

MD(10)