KS57C2308/P2308/C2316/P2316

RESET

9-3

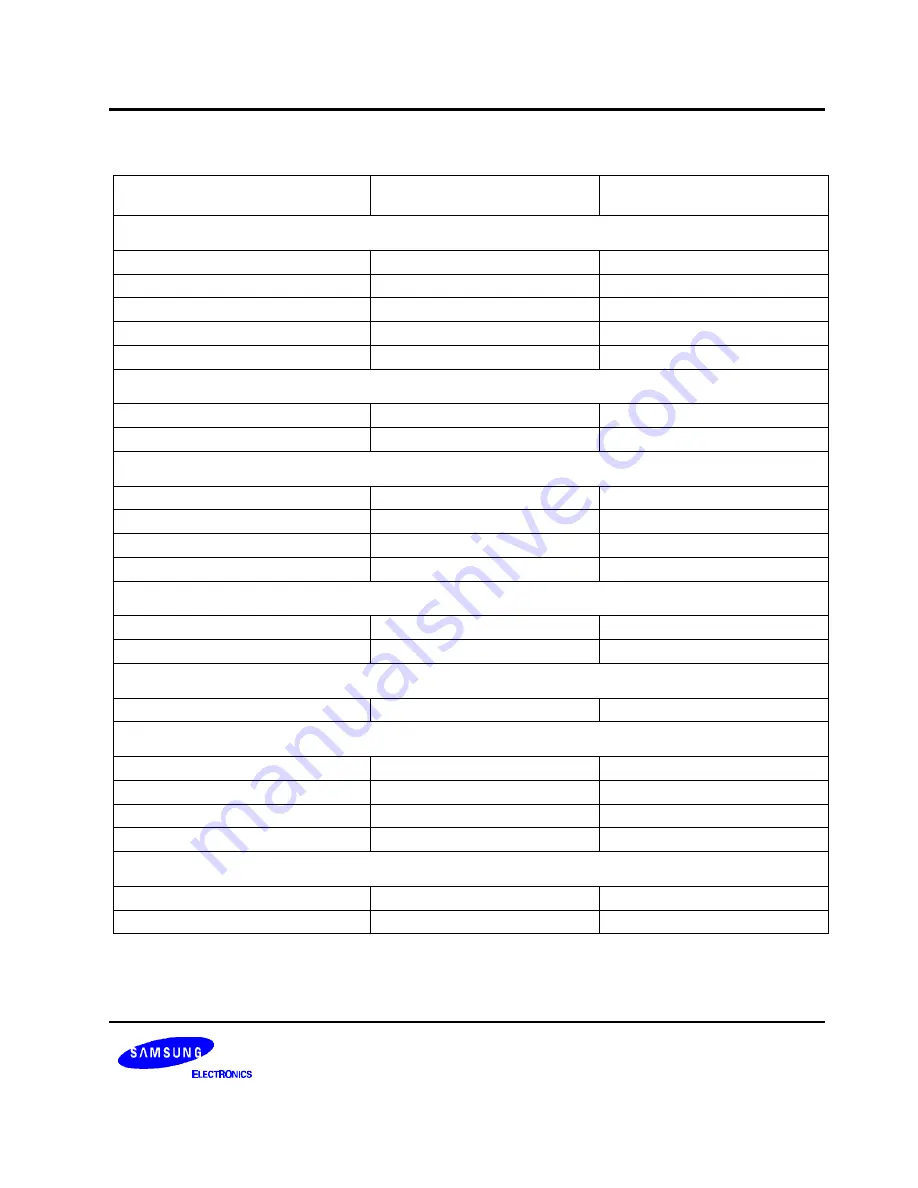

Table 9-1. Hardware Register Values After

RESET

(Continued)

Hardware Component

or Subcomponent

If

RESET

Occurs During

Power-Down Mode

If

RESET

Occurs During

Normal Operation

I/O Ports:

Output buffers

Off

Off

Output latches

0

0

Port mode flags (PM)

0

0

Pull-up resistor mode reg (PUMOD)

0

0

Port N-ch open drain reg (PNE)

0

0

Basic Timer:

Count register (BCNT)

Undefined

Undefined

Mode register (BMOD)

0

0

Timer/Counters 0 and 1:

Count registers (TCNT0)

0

0

Reference registers (TREF0)

FFH

FFH

Mode registers (TMOD0)

0

0

Output enable flags (TOE0)

0

0

Watchdog Timer:

WDT mode register (WDMOD)

A5H

A5H

WDT clear flag (WDTCF)

0

0

Watch Timer:

Watch timer mode register (WMOD)

0

0

LCD Driver/Controller:

LCD mode register (LMOD)

0

0

LCD control register (LCON)

0

0

Display data memory

Values retained

Undefined

Output buffers

Off

Off

Serial I/O Interface:

SIO mode register (SMOD)

0

0

SIO interface buffer (SBUF)

Values retained

Undefined

Содержание C2316

Страница 30: ...ADDRESS SPACES KS57C2308 P2308 C2316 P2316 2 22 NOTES ...

Страница 168: ...SAM47 INSTRUCTION SET KS57C2308 P2308 C2316 P2316 5 94 NOTES ...

Страница 170: ......

Страница 206: ...POWER DOWN KS57C2308 P2308 C2316 P2316 8 8 NOTES ...

Страница 210: ...RESET KS57C2308 P2308 C2316 P2316 9 4 NOTES ...

Страница 222: ...I O PORTS KS57C2308 P2308 C2316 P2316 10 12 NOTES ...

Страница 272: ...LCD CONTROLLER DRIVER KS57C2308 P2308 C2316 P2316 12 24 NOTES ...

Страница 280: ...SERIAL I O INTERFACE KS57C2308 P2308 C2316 P2316 13 8 NOTES ...

Страница 294: ...MECHANICAL DATA KS57C2308 P2308 C2316 P2316 15 2 NOTES ...

Страница 310: ...KS57P2308 P2316 OTP KS57C2308 P2308 C2316 P2316 16 16 NOTES ...

Страница 318: ......

Страница 320: ......

Страница 322: ......

Страница 325: ......

Страница 327: ......