CHAPTER 15 SERIAL INTERFACE IICA

Page 503 of 920

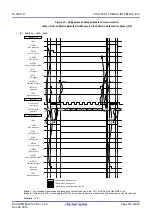

The meanings of <3> to <10> in (2) Address ~ data ~ data in Figure 15 - 41 are explained below.

<3> In the slave device if the address received matches the address (SVAn value) of a slave device

, that slave

device sends an ACK by hardware to the master device. The ACK is detected by the master device (ACKDn =

1) at the rising edge of the 9th clock.

<4> The master device issues an interrupt (INTIICAn: end of address transmission) at the falling edge of the 9th

clock. The slave device whose address matched the transmitted slave address sets a wait status (SCLAn = 0)

and issues an interrupt (INTIICAn: address match)

<5> The master device writes the data to transmit to the IICA shift register n (IICAn) and releases the wait status

that it set by the master device.

<6> If the slave device releases the wait status (WRELn = 1), the master device starts transferring data to the slave

device.

<7> After data transfer is completed, because of ACKEn = 1, the slave device sends an ACK by hardware to the

master device. The ACK is detected by the master device (ACKDn = 1) at the rising edge of the 9th clock.

<8> The master device and slave device set a wait status (SCLAn = 0) at the falling edge of the 9th clock, and both

the master device and slave device issue an interrupt (INTIICAn: end of transfer).

<9> The master device writes the data to transmit to the IICAn register and releases the wait status that it set by the

master device.

<10>The slave device reads the received data and releases the wait status (WRELn = 1). The master device then

starts transferring data to the slave device.

Note

If the transmitted address does not match the address of the slave device, the slave device does not

return an ACK to the master device (NACK: SDAAn = 1). The slave device also does not issue the

INTIICAn interrupt (address match) and does not set a wait status. The master device, however, issues

the INTIICAn interrupt (end of address transmission) regardless of whether it receives an ACK or NACK.

Remark 1.

<1> to <15> in Figures 15 - 40 to 15 - 42 represent the entire procedure for communicating data using

the I

2

C bus. Figure 15 - 40 (1) Start condition ~ address ~ data shows the processing from <1> to <6>,

Figure 15 - 41 (2) Address ~ data ~ data shows the processing from <3> to <10>, and Figure 15 - 42 (3)

Data ~ data ~ stop condition shows the processing from <7> to <15>.

Remark 2.

n = 0, 1

Содержание RL78/G1H

Страница 941: ...R01UH0575EJ0120 RL78 G1H...