119

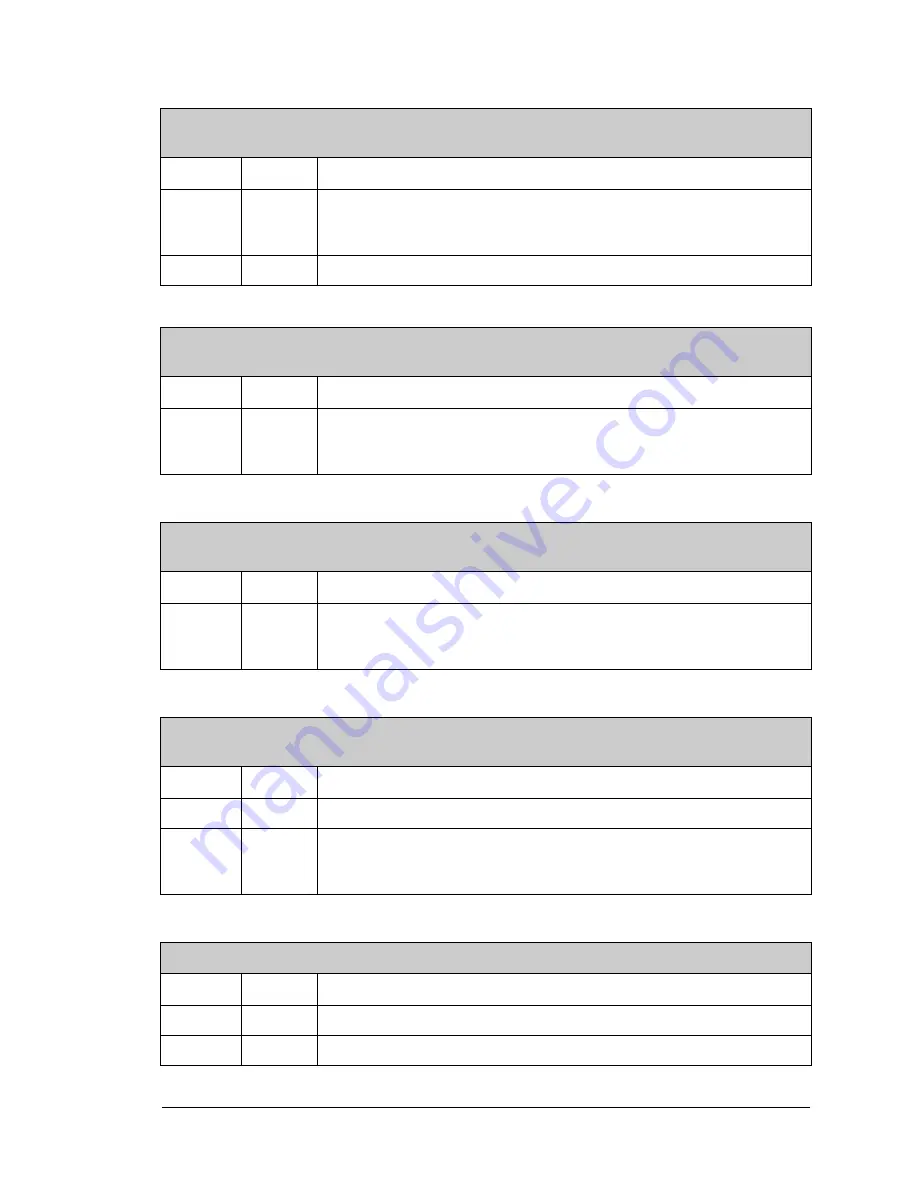

Timer B Count MSB x Register

(TBM1R)

(Address = 0x00B2)

(TBM2R)

(Address = 0x00B4)

Bit(s)

Value

Description

7:6

Two MSBs of the compare value for the Timer B comparator. This compare

value will be loaded into the actual comparator when the current compare detects

a match.

5:0

These bits are reserved and should be written with zero.

Timer B Count LSB x Register

(TBL1R)

(Address = 0x00B3)

(TBL2R)

(Address = 0x00B5)

Bit(s)

Value

Description

7:0

Eight LSBs of the compare value for the Timer B comparator. This compare

value will be loaded into the actual comparator when the current compare detects

a match.

Timer B Step LSB x Register

(TBSL1R)

(Address = 0x00BA)

(TBSL2R)

(Address = 0x00BC)

Bit(s)

Value

Description

7:0

Eight LSBs of the step size for the Timer B comparator. The new compare value

will be loaded into the actual comparator when the current compare detects a

match.

Timer B Step MSB x Register

(TBSM1R)

(Address = 0x00BB)

(TBSM2R)

(Address = 0x00BD)

Bit(s)

Value

Description

7:2

These bits are ignored but should be written with zeros.

1:0

Two MSBs of the step size for the Timer B comparator. The new compare value

will be loaded into the actual comparator when the current compare detects a

match.

Timer B Count MSB Register

(TBCMR)

(Address = 0x00BE)

Bit(s)

Value

Description

7:6

read

The current value of the two MSBs of the Timer B counter are reported.

5:0

These bits are always read as zeros.

Содержание Rabbit 4000

Страница 1: ...Rabbit 4000 Microprocessor User s Manual 019 0152 070720 H...

Страница 18: ...8 Rabbit 4000 Microprocessor User s Manual...

Страница 40: ...30 Rabbit 4000 Microprocessor User s Manual...

Страница 74: ...64 Rabbit 4000 Microprocessor User s Manual...

Страница 82: ...72 Rabbit 4000 Microprocessor User s Manual...

Страница 86: ...76 Rabbit 4000 Microprocessor User s Manual...

Страница 96: ...86 Rabbit 4000 Microprocessor User s Manual...

Страница 182: ...172 Rabbit 4000 Microprocessor User s Manual...

Страница 240: ...230 Rabbit 4000 Microprocessor User s Manual...

Страница 248: ...238 Rabbit 4000 Microprocessor User s Manual...

Страница 256: ...246 Rabbit 4000 Microprocessor User s Manual...

Страница 310: ...300 Rabbit 4000 Microprocessor User s Manual...

Страница 330: ...320 Rabbit 4000 Microprocessor User s Manual...

Страница 348: ...338 Rabbit 4000 Microprocessor User s Manual...