TIMTER™ Multi-mode Digital Telemetry Transmitter

34

Quasonix, Inc.

*SV Note:

Users may save internal clock and data in presets for bench debug use BUT

on a power up or when a

hardware

preset is restored,

CS

and

DS

will be forced to

0

(external clock and data). This action prevents a transmitter from powering up or

changing hardware presets and being set to internal clock and/or data. The ONLY way to

restore CS and/or

DS

as

1

from a saved configuration is by executing the

RC

command.

Note:

All user commands do not apply to all transmitters. Command availability varies depending on the options

ordered and any project specific customization applied. Questions? Please call Quasonix for assistance.

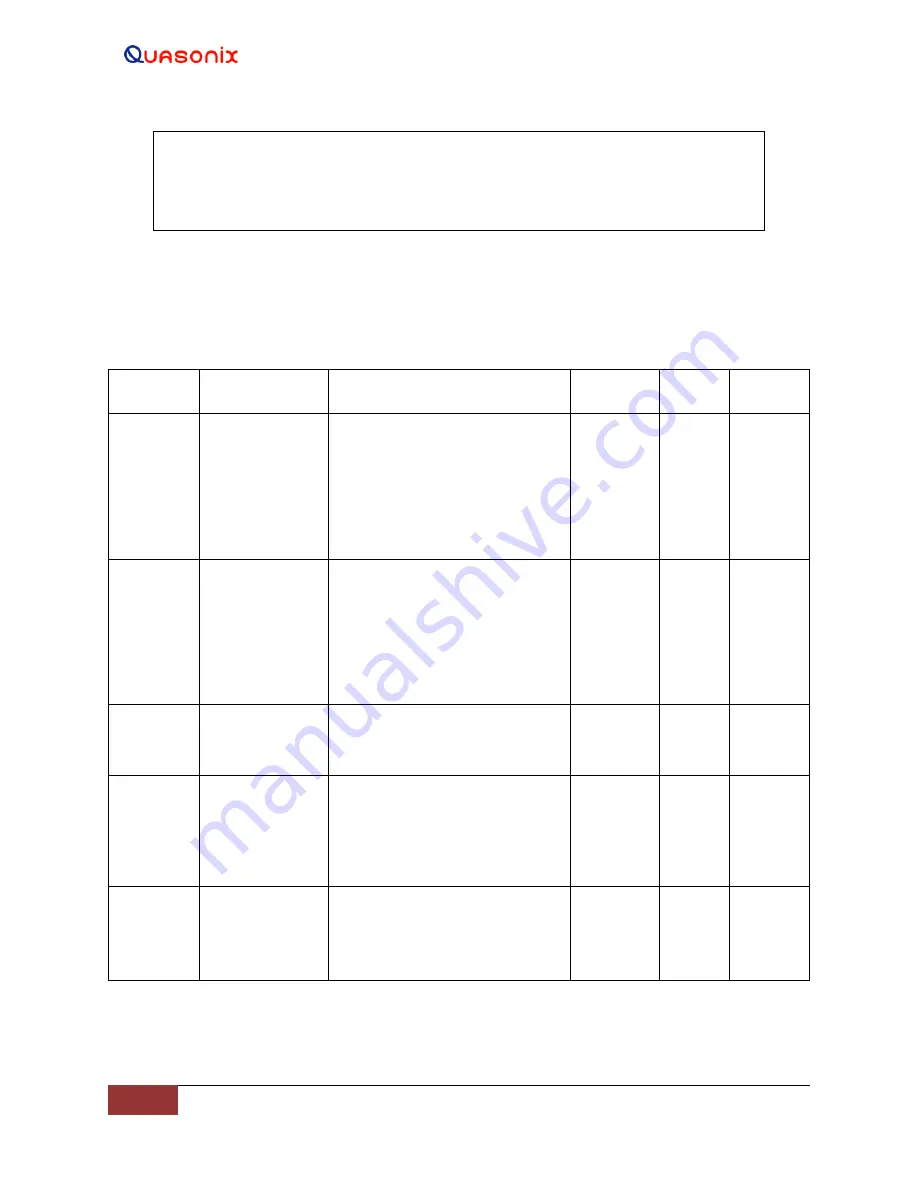

Table 13: Standard and Optional User Commands

Mnemonic

Command

Name

Description

Option (s)

Required

Setting

Saved?

Factory

Default

[

Frequency Step

Down

Left square bracket key retunes

the transmitter to the next lower

frequency, as determined by the

frequency step (FS) parameter

Reply to the control window is the

new frequency, in MHz

No Enter key required

Standard

N/A

N/A

]

Frequency Step

Up

Right square bracket key retunes

the transmitter to the next higher

frequency, as determined by the

frequency step (FS) parameter

Reply to the control window is the

new frequency, in MHz

No Enter key required

Standard

N/A

N/A

?

Help

Displays abbreviated list of

available commands

No Enter key required

Standard

N/A

N/A

<

Step Down

Power

Incrementally steps down the

output power level, from 31 down

to 0

One step per key press

No Enter key required

VP

N/A

N/A

>

Step Up Power

Incrementally steps up the output

power level, from 0 up to 31

One step per key press

No Enter key required

VP

N/A

N/A

Содержание TIMTER QSX-V Series

Страница 39: ...TIMTER Multi mode Digital Telemetry Transmitter 31 Quasonix Inc Figure 22 Baseband Signal Timing ...

Страница 101: ...TIMTER Multi mode Digital Telemetry Transmitter 93 Quasonix Inc Figure 41 Shock Pulse X axis Negative ...

Страница 109: ...TIMTER Multi mode Digital Telemetry Transmitter 101 Quasonix Inc Figure 42 Transmitter Clock and Data Logic ...