CDJ-200

67

5

6

7

8

5

6

7

8

C

D

F

A

B

E

No.

Pin Name

I/O

Pin Function

50

FTE

O

Focus/tracking signal output. (Test pin for servo characteristiv measurement.)

51

RFZI

I

Input for RF ripple zero-cross signal.

52

AVSS3

−

Grounding for analog circuits.

53

RFRP

O

RF ripple signal output.

54

RFDC

O

Pin for the RF peak detection signal supporting hologram.

55

FEI

O

Focus error signal pin.

56

SBAD

O

Subbeam addition signal pin.

57

TEI

O

Tracking error signal pin.

58

TEZI

I

Input for tracking error signal zero-cross.

Power supply for 3.3V analog circuits.

59

AVDD3

−

60

FOO

O

Focus equalizer output.

61

TRO

O

Tracking equalizer output.

62

VREF

O

Reference voltage for analog circuits.

63

FMO

O

Speed error/feed equalizer output.

64

DMO

O

Disc equalizer output.

65

IO2A

O

Unsetting. Always "L"

66

IO3A

O

Unsetting. Always "L"

67

MONIT

O

Pin for monitoring signals in the DSP.

68

FGIN

I

FG signal input for CAV. CLV: "L", CAV: FG input

69

VSS3

−

Grounding for digital circuits.

70

VDD3

−

Power supply for 3.3V digital circuits.

71

TESIN

I

Test input pin, usually fixed at "L" level.

72

XVSS3

−

Grounding for system clock oscillator circuit.

73

XI

I

Input for system clock oscillator circuit.

74

XO

O

Output for system clock oscillator circuit.

75

XVDD3

−

Power supply for 3.3V system clock oscillator circuit.

76

DVSS3

−

Grounding for 1-bit DAC.

77

RO

O

R channel data normal output for 1-bit DAC.

78

DVDD3

−

3.3V power supply for 1-bit DAC.

79

DVR

O

Reference voltage for 1-bit DAC.

80

LO

O

L channel data normal output for 1-bit DAC.

81

DVSS3

−

Grounding for 1-bit DAC.

82

ZDET

O

Zero detection flag output for 1-bit DAC.

83

VSS5

−

Grounding for interface.

84

BUS0

I/O

Data input/output for the microcomputer interface

85

BUS1

I/O

Data input/output for the microcomputer interface

86

BUS2

I/O

Data input/output for the microcomputer interface

87

BUS3

I/O

Data input/output for the microcomputer interface

88

BUCK

I

Clock input for the microcomputer interface

89

/CCE

I

Chip enable signal input for the microcontroller interface. BUS3 to BUS0 are active if this pin is "L".

90

/RST

I

Reset signal input. The internal registers and servo section registers are reset, respectively, when

the reset signal is "L" and on the rising edge of the reset signal.

91

VDD5

−

Power supply for the interface,

92

IO0B (TEZC)

O

The signal that inverts H/L with TE zero-cross.

93

IO1B (DFCT)

O

Defect signal. Normally "H", but it becomes "L" when detecting dirts on the disc.

94

IO2B (TRSR)

O

It becomes "L" during tracking close or search.

95

IO3B (HYS)

O

It becomes "L" in the hysteresis operation.

96

EMPH

O

Emphasis flag output. EMPH ON: "H", EMPH OFF: "L" The output polarity is switched, using a command.

97

BCK

O

Bit clock output. 32fs, 48fs and 64fs are selected, using a command.

98

AOUT

O

Audio data output. Which bit is first (MSB first or LSB first) can be selected, using a command.

99

LRCK

O

LR channel clock output. L ch: "L", R ch: "H" The output polarity can be inverted, using a command.

100 DOUT

O

Digital-out output

Содержание CDJ-200

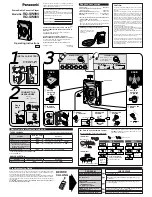

Страница 22: ...CDJ 200 22 1 2 3 4 1 2 3 4 C D F A B E 3 4 MAIN ASSY 2 2 A 2 2 A 2 2 MAIN ASSY DWG1587 2 2 A 2 2 A ...

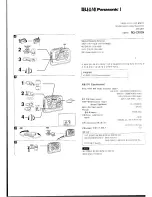

Страница 26: ...CDJ 200 26 1 2 3 4 1 2 3 4 C D F A B E 3 7 JACK ASSY I JACK ASSY DWX2433 I CN104 A 1 2 ...

Страница 27: ...CDJ 200 27 5 6 7 8 5 6 7 8 C D F A B E I L R AUDIO OUT PHONES AUDIO SIGNAL ROUTE L ch ...

Страница 79: ...CDJ 200 79 5 6 7 8 5 6 7 8 C D F A B E ...