CD-UB100/XN/UC

31

5

6

7

8

5

6

7

8

C

D

F

A

B

E

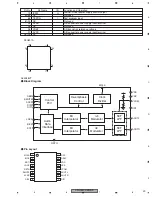

TCC8600-00X-EA-AG

128

33

64

97

32

65

96

1

Pin No.

Pin Name

I/O

Function and Operation

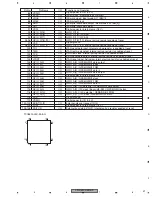

85

86

87

88

89

90

91

92

93

94

95,96

97

98,99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

118

119

120-123

124

125-128

VDDIO

BCLK

LRCK

MCLK

DAO

DAI

VDDI

GPIO_D[15]

GPIO_D[16]

GPIO_D[17]

GPIO_D[18],[19]

VSS

GPIO_D[20],[21]

TDI

TMS

TCK

TDO

nTRST

GPIO_A[0]

GPIO_A[1

GPIO_A[2]

GPIO_A[3]

GPIO_A[4]

VDDI

GPIO_A[5]

GPIO_A[6]

GPIO_A[7]

GPIO_A[8]

GPIO_A[9]

GPIO_A[10]

GPIO_A[11]

VSS

VDDIO

EXINT[0]-[3]

VDDI

XD[0]-[3]

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Digital power for I/O (3.3 V)

I2S bit clock / Boot mode bit 0 (BM[0])

I2S word clock / Boot mode bit 1 (BM[1])

I2S System Clock

I2S digital audio data output / Boot mode bit 2 (BM[2])

I2S digital audio data input

Digital power for internal core (1.8 V)

GPIO_D[15]

GPIO_D[16] / I2C SDA

GPIO_D[17] / I2C SCL

GPIO_D[18], [19]. Internal pull-up resistor enabled at reset.

Digital ground

GPIO_D[21], [20]. Internal pull-up resistor enabled at reset.

JTAG serial data input. Internal pull-up resistor is enabled at reset

JTAG test mode select. Internal pull-up resistor is enabled at reset

JTAG test clock. Internal pull-up resistor is enabled at reset

JTAG serial data output. Internal pull-up resistor is enabled at reset

JTAG reset signal. Active low. Internal pull-up resistor is enabled at reset

GPIO_A[0] / GPSB/GSIO1 data output

GPIO_A[1] / GPSB/GSIO1 clock

GPIO_A[2] / GPSB/GSIO1 FRM

GPIO_A[3] / GPSB/GSIO1 data in

GPIO_A[4] / GPSB/GSIO1 data output

Digital power for internal core (1.8 V)

GPIO_A[5] / GPSB/GSIO1 clock

GPIO_A[6] / GPSB/GSIO1 FRM

GPIO_A[7] / GPSB/GSIO1 data in

GPIO_A[8] / I2C data line / GPSB/GSIO3 data output

GPIO_A[9] / I2C clock./ Bus width (BW) / GPSB/GSIO3 clock

GPIO_A[10] / I2C data line / GPSB/GSIO3 FRM

GPIO_A[11] / I2C clock / GPSB/GSIO3 data in

Digital ground

Digital power for I/O (3.3 V)

External interrupt request [0]-[3]

Digital power for internal core (1.8 V)

External bus data bit [0]-[3]. Internal pull-up resistor enabled at reset.

Содержание CD-UB100

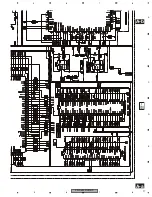

Страница 5: ...CD UB100 XN UC 5 5 6 7 8 5 6 7 8 C D F A B E 1 SPECIFICATIONS ...

Страница 14: ...CD UB100 XN UC 14 1 2 3 4 1 2 3 4 C D F A B E A a A b A b 1 1 8 mH A MOTHER UNIT ...

Страница 16: ...CD UB100 XN UC 16 1 2 3 4 1 2 3 4 C D F A B E A b A a A a A b 1 C953 470P C952 R001 L610 120 180 220 ...

Страница 17: ...CD UB100 XN UC 17 5 6 7 8 5 6 7 8 C D F A B E A a A b A b A a 220 0R0 R632 47K ...

Страница 19: ...CD UB100 XN UC 19 5 6 7 8 5 6 7 8 C D F A B E A SIDE A 70 80 90 100 110 120 130 140 FRONT IN POWER SUPPLY ...

Страница 20: ...CD UB100 XN UC 20 1 2 3 4 1 2 3 4 C D F A B E A A MOTHER UNIT 70 80 90 100 110 120 130 140 R632 L61 ...

Страница 21: ...CD UB100 XN UC 21 5 6 7 8 5 6 7 8 C D F A B E A SIDE B 10 20 30 40 50 60 70 10 20 30 40 50 60 70 80 0 X Y L610 ...

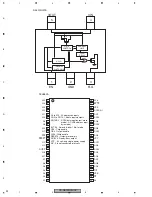

Страница 36: ...CD UB100 XN UC 36 1 2 3 4 1 2 3 4 C D F A B E 8 OPERATIONS ...

Страница 37: ...www mobiteh com ...