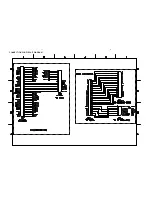

ES3210 PINOUT

ES3210 PIN DESCRIPTION

1

VSS

AUX4

AUX3

AUX2

AUX1

AUX0

PCLK

PCLK2X

CPUCLK

HSYNC

VSYNC

YUV7

YUV6

YUV5

YUV4

YUV3

YUV2

YUV1

YUV0

VDD

VPP

LA12

LA13

LA14

LA15

LA16

LA17

ACLK

AOUT/SEL_PLL0

ATCLK

ATFS/SEL_PLL1

DOE#

AIN

ARCLK

ARFS

TDMCLK

TDMDR

TDMFS

CAS#

VSS

DBUS8

DBUS7

DBUS6

DBUS5

DBUS4

DBUS3

DBUS2

DBUS1

DBUS0

MA

8

MA

7

MA

6

MA

5

MA

4

MA

3

MA

2

MA

1

MA

0

RAS#

VDD

VS

S

RESET#

DWE#

DBUS14

DBUS15

DBUS1

3

DBUS1

2

DB

U

S

1

1

DBUS1

0

DBUS9

LD6

LD

7

LW

R

#

LO

E

#

LCS3#

LC

S

1

#

LC

S

0

#

LA0

LA

1

LA2

LA

3

LA

4

LA5

LA

6

LA

7

LA8

LA

9

LA10

LA

1

1

VSS

VDD

AUX6

AUX5

AUX7

LD

0

LD1

LD2

LD3

LD

4

LD

5

31

30

51

50

80

81

100

2

3

4

5

6

7

8

9

10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

79 78 77 76 75 74 73 72 71 70 69 68 67 66 65 64 63 62 61 60 59 58 57 56 55 54 53 52

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

ES3210

100-pin PQFP

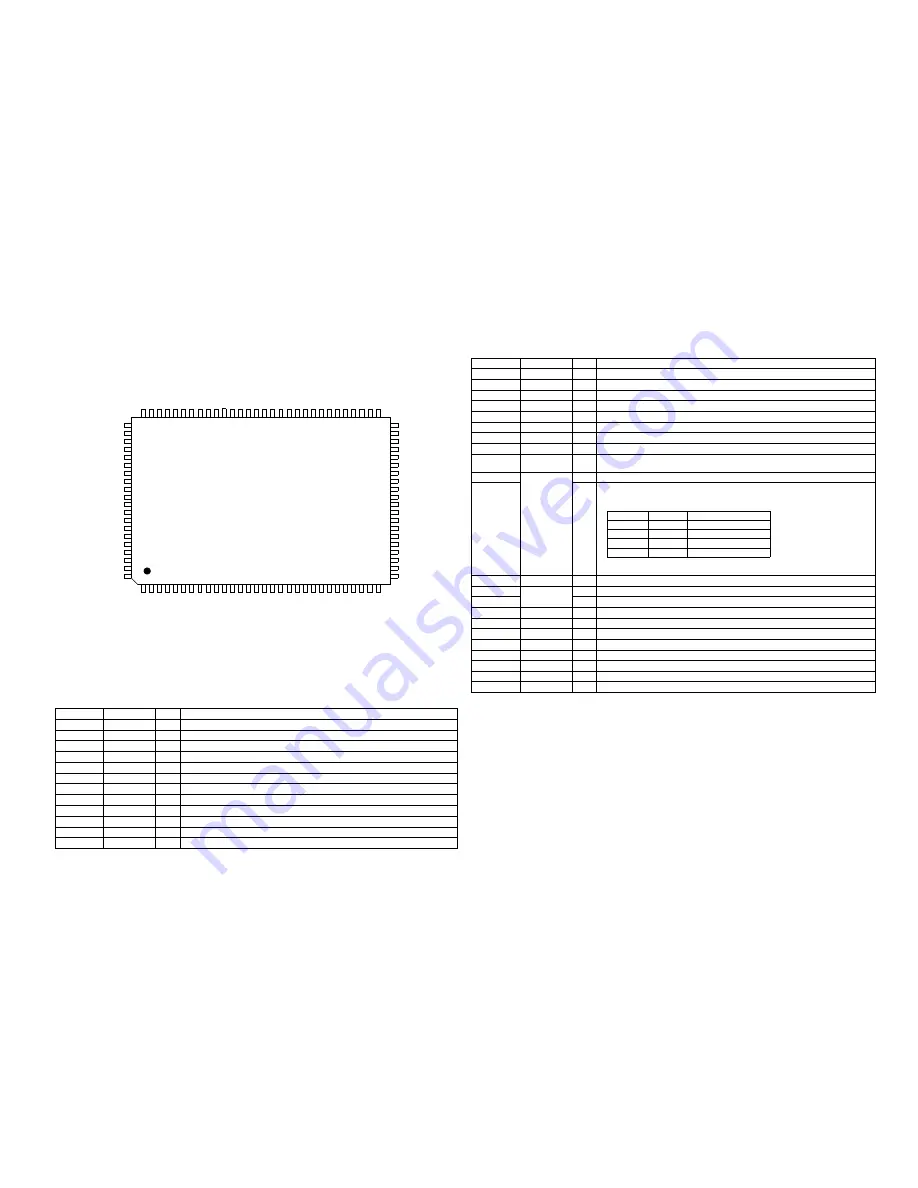

Name

Number

I/O

Definition

VDD

1, 31, 51

I

Voltage supply for 3.3V.

RAS#

2

O

DRAM row address strobe (active low).

DWE#

3

O

DRAM write enable (active low).

MA[8:0]

12:4

O

DRAM multiplexed row and column address bus.

DBUS[15:0]

28:13

I/O

DRAM data bus I/O [15:0].

RESET#

29

I

System reset (active low).

VSS

30, 50, 80, 100

I

Ground.

YUV[7:0]

39:32

O

YUV[7:0] pixel output data.

VSYNC

40

I/O

Vertical sync for screen video interface, programmable for rising or falling edge.

HSYNC

41

I/O

Horizontal sync for screen video interface, programmable for rising or falling edge.

CPUCLK

42

I

RISC and system clock input. CPUCLK is used only if SEL_PLL[1:0] = 00.

PCLK2X

43

I/O

Pixel clock; two times the actual pixel clock for screen video interface.

PCLK

44

I/O

Pixel clock qualifier in for screen video interface.

AUX[7:0]

54:52, 49:45

I/O

Auxiliary control pins (AUX0 and AUX1 are open collectors).

LD[7:0]

62:55

I/O

RISC interface data bus.

LWR#

63

O

RISC interface write enable (active low).

LOE#

64

O

RISC interface output enable (active low).

LCS[3,1,0]#

65:67

O

RISC interface chip select (active low).

LA[17:0]

87:82, 79:68

O

RISC interface address bus.

VPP

81

I

Digital supply voltage for 5V.

ACLK

88

I/O

Master clock for external audio DAC (8.192 MHz, 11.2896 MHz, 12.288 MHz, 16.9344

MHz, and 18.432 MHz).

AOUT/

89

O

Dual-purpose pin. AOUT is the audio interface serial data output

SEL_PLL0

I

Select PLL[0] input. The matrix below lists the available clock frequencies and their

respective PLL bit settings.

ATCLK

90

I/O

Audio transmit bit clock.

ATFS

91

O

Audio transmit frame sync.

SEL_PLL1

I

Refer to the description and matrix for SEL_PLL0 pin 89.

DOE#

92

O

DRAM output enable (active low).

AIN

93

I

Audio serial data input.

ARCLK

94

I

Audio receive bit clock.

ARFS

95

I

Audio receive frame sync.

TDMCLK

96

I

TDM interface serial clock.

TDMDR

97

I

TDM interface serial data receive.

TDMFS

98

I

TDM interface frame sync.

CAS#

99

O

DRAM column address strobe bank 0 (active low).

Name

Number

I/O

Definition

SEL_PLL1 SEL_PLL0 Clock Output

0

0

Bypass PLL

0

1

54.0 MHz

1

0

67.5 MHz

1

1

81.0 MHz

PIN DESCRIPTION (Continued)

VIDEO CD PROCESSOR

ES3210

VIDEO CD PROCESSOR

ES3210

8-5

8-5

Содержание MC-M350 SERIES

Страница 12: ...2 2 2 2 ...

Страница 14: ...4 1 4 1 SET WIRING DIAGRAM ...

Страница 16: ...CIRCUIT DIAGRAM FRONT BOARD 5 2 5 2 ...

Страница 17: ...LAYOUT DIAGRAM FRONT BOARD COMPONENT SIDE 5 3 5 3 LAYOUT DIAGRAM FRONT BOARD SMD SIDE ...

Страница 19: ...POWER BOARD TABLE OF CONTENTS CircuitDiagram 6 2 PCB Layout 6 3 Electrical PartsList 6 4 6 1 6 1 ...

Страница 20: ...6 2 6 2 CIRCUIT DIAGRAM ...

Страница 21: ...6 3 6 3 POWER PCB LAYOUT ...

Страница 24: ...AM FM TUNER IC TA2149BN AM FM TUNER IC TA2149BN BLOCK DIAGRAM Pins Description 7 2 7 2 ...

Страница 25: ...AM FM TUNER IC TA2149BN Pins Description Pins Description AM FM TUNER IC TA2149BN 7 3 7 3 ...

Страница 26: ...AM FM TUNER IC TA2149BN Pins Description AM FM TUNER IC TA2149BN Pins Description 7 4 7 4 ...

Страница 27: ...AM FM IF FM STEREO DETECTOR TA2099N BLOCK DIAGRAM Pins Description AM FM IF FM STEREO DETECTOR TA2099N 7 5 7 5 ...

Страница 31: ...DIGITAL TUNING IC TC9257F DIGITAL TUNING IC TC9257F 7 9 7 9 ...

Страница 32: ...CIRCUIT DIAGRAM TUNER BOARD NON CENELEC 7 10 7 10 ...

Страница 34: ...7 12 7 12 CIRCUIT DIAGRAM TUNER BOARD CENELEC ...

Страница 35: ...LAYOUT DIAGRAM TUNER BOARD CENELEC COMPONENT SIDE LAYOUT DIAGRAM TUNER BOARD CENELEC COPPER SIDE 7 13 7 13 ...

Страница 38: ...MICROPROCESSOR TMP87EP26F MICROPROCESSOR TMP87EP26F BLOCK DIAGRAM 8 2 8 2 PINS DESCRIPTION ...

Страница 39: ...8 3 8 3 MICROPROCESSOR TMP87EP26F PINS DESCRIPTION POWER DRIVER IC TA2092N ...

Страница 42: ...DIGITAL SERVO PROCESSOR TC9462F BLOCK DIAGRAM 8 6 8 6 ...

Страница 43: ...DIGITAL SERVO PROCESSOR TC9462F DIGITAL SERVO PROCESSOR TC9462F PINS DESCRIPTION PINS DESCRIPTION 8 7 8 7 ...

Страница 44: ...DIGITAL SERVO PROCESSOR TC9462F PINS DESCRIPTION DIGITAL SERVO PROCESSOR TC9462F PINS DESCRIPTION 8 8 8 8 ...

Страница 46: ...MICROPROCESSOR TA2153FN BLOCK DIAGRAM 8 10 8 10 ...

Страница 47: ...CIRCUIT DIAGRAM MCU CD BOARD 8 11 8 11 ...

Страница 48: ...LAYOUT DIAGRAM MCU CD BOARD COMPONENT SIDE 8 12 8 12 ...

Страница 49: ...8 13 8 13 LAYOUT DIAGRAM MCU CD BOARD SMD SIDE ...

Страница 52: ...9 2 9 2 CONNECTION PCB CIRCUIT DIAGRAM ...

Страница 53: ...9 3 9 3 CONNECTION PCB LAYOUT DIAGRAM ...

Страница 58: ...MAIN BOARD CIRCUIT DIAGRAM 10 4 10 4 ...

Страница 59: ...10 5 10 5 TAPE PART CIRCUIT DIAGRAM ...

Страница 60: ...MAIN PCB COMPONENT LAYOUT 10 6 10 6 ...

Страница 61: ...MAIN PCB SMD LAYOUT 10 7 10 7 ...