9-2

9-2

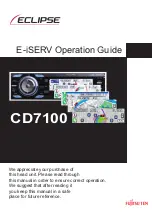

BLOCK DIAGRAM

Deck B (Rec/Pb) switches, sensors & motor

4x

DECK(S) SW.

STATUS TO

VOLTS CONV.

2x

SOLENOID

SUPPLY CTRL

SOLENOID

SUPPLY CTRL

MOTOR VCC

SUPPLY CTRL

NS/HS CTRL

Deck

A

(Pb) switches, sensors & motor

NOM/HI SPEED

REC EON.

IEC I IEC II

REC EON.

REC EON. SW.

HEF4952BT

RECORD AMP

NJM4560D

OSCILLATOR

REC

CRB

Line-In

Playback

Head

Rec/Pb

Head

Erase

Head

BIAS SYM

HD SW.

BIAS ADJ

Erase

Bias

REC

ALCEN

PRE-AMPLIFIER

AN7318S

SOURCE SEL

HEF4952BT

1A0 1A1 1A2

Rec current

ATTEN

ALC

PLAYBACK

EQUALISATION

PB EON. SW.

HEF4952BT

2A0 2A1 2A2

MPX

1A0

1A1

PB A ADJ

PB B ADJ

Rec In

PB In

2A2

DOLBY B NR

CXA1101M

REC Out

PB Out

REC ADJ

SHIFT

REGISTER

HEF4094BT

3A0 3A1 3A2

(HS) (REC) (CRB)

DOLBY

NOM/HI SPEED

REC EON.

3A0 NS

2A2

MUTE

For Dolby version only

PB Out

ATTEN

4794 #

9792 #

#

CLK

DATA

STROBE

# For Non-dolby version only

Only 1 channel is presented.

NOTE:

MicroProcessor Control / Communication lines

Direct / Indirect Control lines from Shift Registers

AD1 AD2

1A2

1A1

ALCEN

1A0

REC

7787

7791

7780

7710

7720

7740

7730

7630

7640

1A0

2A1

2A2

REC

NS/HS (NS)

HS

NS/HS

(NS)

3A0

2A0

CRA

7792

7622

7788

7610