3DQDVRQLF

44

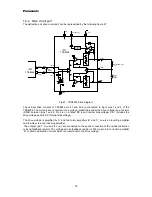

2)CHROMINANCE SIGNAL PROCESSING (PB)

Pre-amp

7th pin

15

Chrominance Signal Processing (Playback)

50

Phase Comp.

AGC Amp.

2H Delay

Amp.

15

13

NAP

LPF

Y/C Mix

BPF2

46

BPF1

48

1

3

52

LPF

Kill

BPF

45

CNC

(LC89978M)

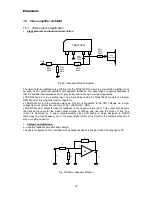

The down converted chrominance signal is obtained from PB ENVE signal by LPF first.

And then the signal is up-converted to 4.43MHz by the MAIN CONVERTER.

The redundant harmonics is filtered out by the BPF, and then the signal is applied to the CCD IC to reduce

the chrominance crosstalk.

The NTSC PLAYBACK is possible on PAL/SECAM SYSTEM by the NAP circuit, the activation of which is

determined by GROUP 7, MSB 7-8bits.

The signal is then applied to Color Noise Canceller and mixed together with the luminance signal.