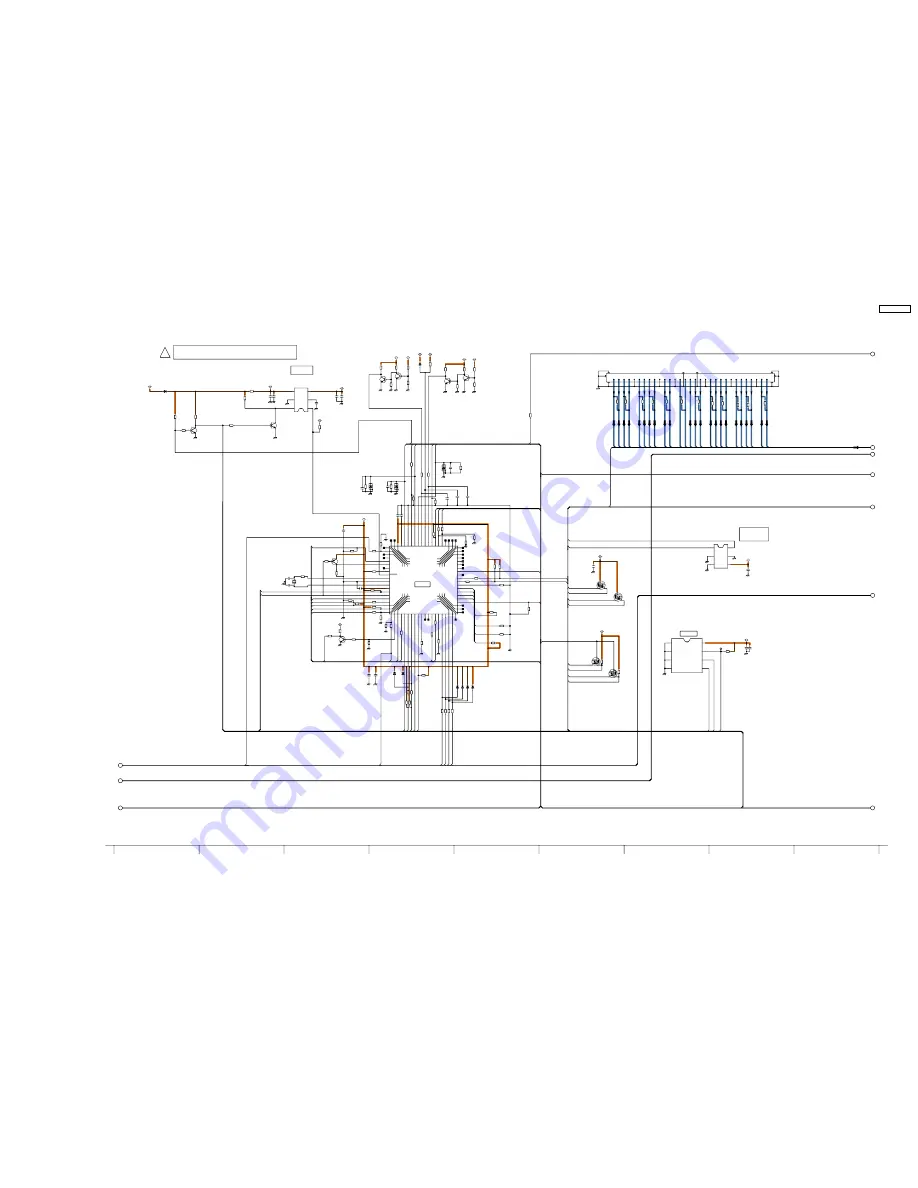

15.45. D-Board (2 of 8) Schematic Diagram

RCLK_E-

M_SEL1

LVDSBIT

P3V_SCL1

SOS9_CONF

RA_0+

RA_E-

P3V_SDA1

INEXCH

ALARM

RB_0-

RA_E+

STB_SCL01

RB_0+

SOS8_SS

EEP_WR_CTL

STB_SCL01

M_SEL4

RB_E-

SOS4_PS

STB_SDA01

XRST

XRST

M_SEL3

RC_0-

AR_IIC_INT

P

ANEL_MAIN_ON

RB_E+

STB_SDA01

REM_IN

RC_0+

P_ON/OFF

RC_E-

P

ANEL_STBY_ON

SOS9_CONF

RD_0-

READY

M_SEL3

M_SEL2

LED_R

NRST

RC_E+

STBY3.3V_ON

M_SEL2

PANASONIC_MODE

RD_0+

LED_G

RD_E-

RE_0-

RD_E+

TXD_PC

RE_0+

RCLK_0-

M_SEL4

RE_E-

L

VDS_DET

STB_SD

A02

P3V_SDA02

P3V_SCL02

STB_SCL02

P3V_SCL02

XRST

STB_SCL02

P3V_SDA02

STB_SDA02

RE_E+

RA_0-

DRVRST

SOS6_SC1

VD

A

T

A_DET

L

VDS_DET

DCLK

D

ATA

0

ASDIO

NCS

STB_SCL02

STB_SD

A02

FVSEL

AR_IIC_CONT

AR_IIC_CONT

L

VDS_DET

C_SEL

SOS7_SC2

XRST2

EEP_WR_CTL

RXD_PC

XRST

M_SEL1

R9060

100

R9156

10k

Q9058

B1CBHD000002

D9110

B0JCGD000002

R9218

10k

R9175

10k

R9237

10k

R9160

0

R9109

10k

R9141

100

D9102

B0JCGD000002

STB3.3V

R9149

4.7k

Q9044

B1ABCF000138

D9105

B0JCGD000002

R9155

5.6k

R9221

10k

R9204

4.7k

R9074

100

R9134

33k

TVRP068-6

IC9003

1

2

3

4

5

6

CNV

7

8

-

9

RESET

10

XOUT

11

VSS

12

XIN

13

VCC

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

IC9011

C0EBF0000431

1

RESET

2

Cd

3

VOUT

4

VDD

5

GND

6

CE

R9188

5.6k

STB5V

R9169

10k

STB3.3V

R9064

100

R9105

100

D9100

B0JCGD000002

R9066

100

R9203

1k

IC9001

TVRP509-1

1

A0

2

A1

3

A2

4

GND

5

SDA

6

SCL

7

WP

8

Vcc

C9058

6.3V

10u

R9206

1k

D9019

MAZ303300L

R9174

10k

C9045

16V

0.1u

R9185

22

R9189

10k

R9120

100

R9094

10k

R9113

10

R9143

100

R9192

0

C9056

16V

0.1u

R9067

100

R9178

10k

R9062

100

R9101

10k

Q9201

B1CBHD000002

R9220

10k

D9101

B0JCGD000002

C9053

16V

0.1u

R9107

3.3k

Q9200

B1CBHD000002

P3.3V

C9052

16V

0.1u

C9033

16V

0.1u

Q9051

B1ABCF000138

X9000

H2D200500011

R9194

0

STB3.3V

R9061

100

R9176

10k

R9166

10k

R9182

1k

Q9050

B1ABCF000138

R9165

10k

C9050

16V

0.1u

C9046

16V

0.1u

D5

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

R9171

39k

R9127

68k

R9170

39k

R9209

10

R9158

10k

STB3.3V

Q9052

B1ABCF000138

R9205

4.7k

Q9054

B1ABCF000138

R9199

2.7k

C9039

6.3V

10u

R9247

4.7k

R9190

10k

C9044

16V

0.1u

C9048

16V

0.1u

D9018

MAZ303300L

R9207

1k

STB3.3V

R9151

22

STB3.3V

R9065

100

R9222

10k

C9037

0.01u

50V

R9248

4.7k

C9049

16V

0.1u

TP9000

R9121

100k

R9187

5.6k

R9177

22k

R9150

22

R9063

100

*R9098

10k

R9183

1k

R9210

2.7k

R9167

100

R9179

1k

C9034

16V

0.1u

P3.3V

R9108

10k

STB3.3V

R9161

0

R9186

22

R9110

0

D9103

B0JCGD000002

R9148

10k

R9145

100

C9051

16V

0.1u

C9055

16V

0.1u

R9236

0

D9017

MAZ303300L

Q9057

B1CBHD000002

C9040

16V

0.1u

R9129

68k

R9140

0

STB3.3V

Q9049

B1ADCE000011

R9159

10k

IC9002

C0ZBZ0001330

1

SCL

2

GND

3

ADD1

4

V+

5

ADD0

6

SDA

R9181

1k

R9196

10k

R9184

1k

R9217

10k

R9144

100

R9102

100

C9057

16V

0.1u

R9193

10k

Q9046

B1ABCF000138

R9154

5.6k

P15V

R9215

12k

P5V

STB5V_M

C9035

6.3V

10u

P3.3V

D9020

MA2J72800L

C9036

6.3V

10u

R9180

10k

C9047

16V

0.1u

Q9053

B1ABCF000138

P3.3V

D9106

B0JCGD000002

R9076

100

R9219

10k

R9172

39k

R9111

22k

*R9097

10k

*R9157

10k

IIC_CONT

NC

GND

DRIVER_RESET

SCLK(f

or Loader)

IIC1_SCL

SOS8_SS

NC

CE(Loader)

E+ L

VDS2

NC

O+ L

VDS3

E+ L

VDS1

SOS4_PS

GND

XRST

O+ L

VDS0

RESET

IIC1_SDA

B

USY(f

or Loader)

NC

A

VSS

GND

NC

NC

E- L

VDS2

FPGA_CE

NC

SOS7_SC2

NC

XOUT

REM_IN

SOUT(FPGA)

GND

NC

O- L

VDS3

NC

VREF

FVSEL

E+ L

VDS3

PLL_RST

M_SEL2

SIN(FPGA)

NC

LSI_RST

E- L

VDS3

M_SEL3

O+ L

VDS1

ALARM

INEXCH

E+ L

VDS4

A

C_GOOD

O- L

VDS1

P_ON/OFF

GND

NC

E- L

VDS4

L

VDS_DET

E+ L

VDSCLK

SOS6_SC1

O+ L

VDS2

NC

AVCC

O- L

VDS2

VSS

P

ANEL_MAIN_ON

NC

E- L

VDS0

SOS9_CONF

GND

SCLK(FPGA)

EEP_WR_CTL

NC

O+ L

VDS4

LED_GRN

O- L

VDS4

IIC_INT

E+ L

VDS0

M_SEL4

NC(ALL_OFF)

IIC2_SCL

SOS_INH

SOS5_5V

XIN

NC

NC(C_SEL)

IIC2_SD

A

P

ANASONIC_MODE

O- L

VDSCLK

LVDS_MODE

NC

NC

O+ L

VDSCLK

VCC

E- L

VDSCLK

NC

TXD(Loader)

O- L

VDS0

LVDS_BIT

SOS3_3V

READY

RXD(Loader)

INT_CONF

E- L

VDS1

LED_RED

SOS2_15V

CNVSS

M_SEL1

NC

MAIN_CONF

VD

A

T

A_DET

EEPROM

RESET

STB 3.3V

MICOM

TEMPERATURE

DIGITAL

SENSOR

1

2

3

11

12

17

16

14

15

13

16

17

13

11

12

10

14

18

15

TO

DH-BOARD

(DH5)

!

D-BOARD TZTNP01LXTU (2/8)

TH-50PZ750U

D-Board (2 of 8) Schematic Diagram

TH-50PZ750U

D-Board (2 of 8) Schematic Diagram

TH-50PZ750U

121

Содержание TH50PZ750U - 50" Plasma TV

Страница 5: ...1 Applicable signals 5 TH 50PZ750U ...

Страница 21: ...8 Location of Lead Wiring 8 1 Lead of Wiring 1 21 TH 50PZ750U ...

Страница 22: ...8 2 Lead of Wiring 2 22 TH 50PZ750U ...

Страница 23: ...8 3 Lead of Wiring 3 23 TH 50PZ750U ...

Страница 24: ...8 4 Lead of Wiring 4 24 TH 50PZ750U ...

Страница 25: ...8 5 Lead of Wiring 5 25 TH 50PZ750U ...

Страница 26: ...8 6 Lead of Wiring 6 26 TH 50PZ750U ...

Страница 27: ...8 7 Lead of Wiring 7 27 TH 50PZ750U ...

Страница 31: ...9 4 No Picture 31 TH 50PZ750U ...

Страница 38: ...11 4 Adjustment Volume Location 11 5 Test Point Location 38 TH 50PZ750U ...

Страница 40: ...40 TH 50PZ750U ...

Страница 42: ...NOTE 42 TH 50PZ750U ...

Страница 76: ...NOTE TH 50PZ750U 76 ...

Страница 77: ...15 Schematic and Block Diagram 15 1 Schematic Diagram Note TH 50PZ750U 77 ...

Страница 154: ...NOTE TH 50PZ750U 154 ...

Страница 155: ...16 Exploded Views Replacement Parts List 16 1 Exploded Views 155 TH 50PZ750U ...

Страница 156: ...16 2 Packing Exploded Views Accessories 156 TH 50PZ750U ...

Страница 157: ...16 3 Packing Exploded Views Stand 157 TH 50PZ750U ...

Страница 158: ...16 4 Replacement Parts List Notes 158 TH 50PZ750U ...