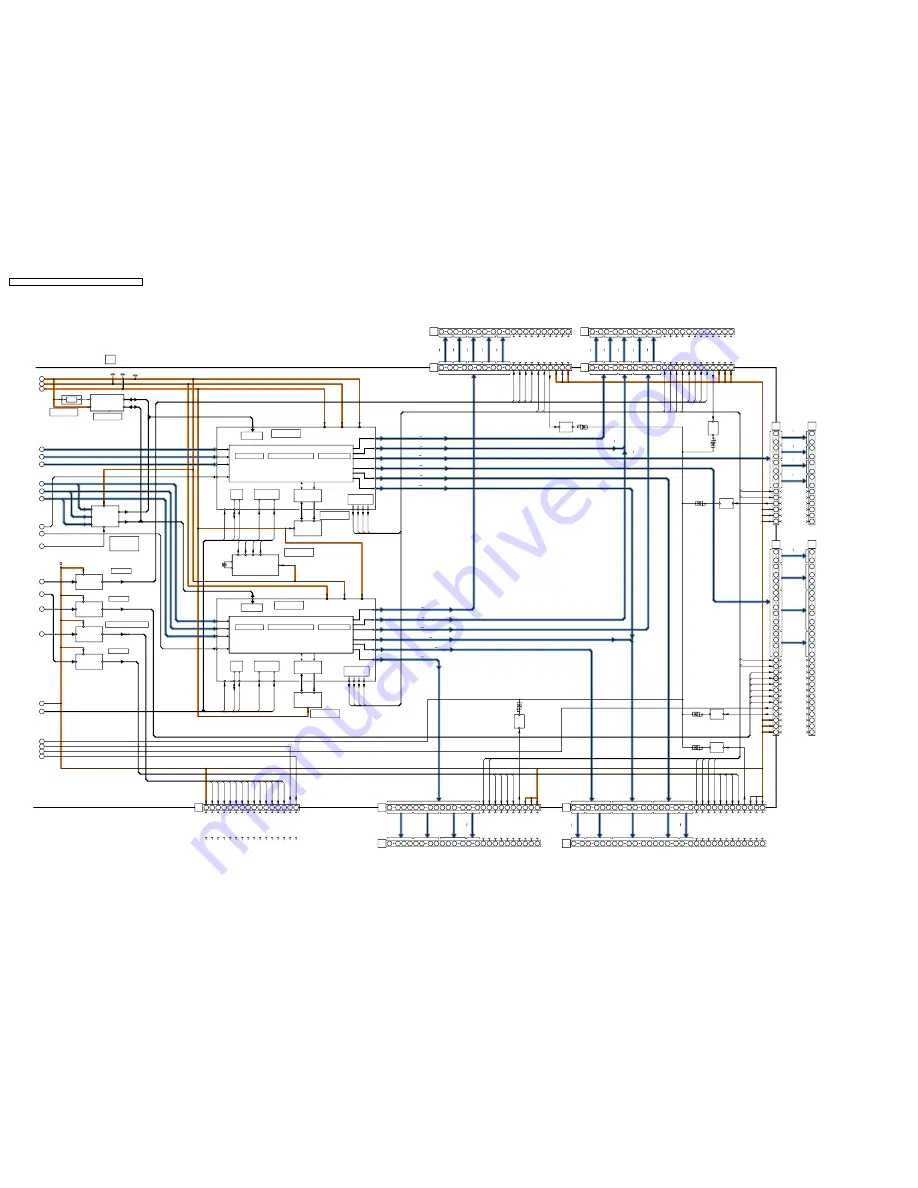

15.48. D-Board (2 of 2) Block Diagram

CL

SD

A2

CSL

SIU

CPH

PRCK

SCSU

SD

A2

CLKM

CML

CEL

SCL2

PCK

CEH

CEL2

CSH

OCK

SCL2

SID

CMH

CLK

D9302

D9300

D9301

P+2.5V

D9304

P+5V

P+3.3V

D9305

P+1.2V

D9303

(D16B,D16C,D18A

D21C)

CLKU1(-)

P+5V

61

DATA CONTROL 8bit

1

CLK

CLR

U1

P+5V

57

19

DATA 14Bit

26

CLKD5(-)

U29A

+5V DET

LEU2

1

50

P+3.3V

26

63

10bit

CLKU3(-)

UMH

84MHz

CLKD1(-)

CLKU3(-)

34

P+2.5V

NUEL

UML

IC9200

IC9400

10bit

61

CLKU2(+)

36

42

11

IC9802,IC9803

D17A-D17C

60

25

26

2

DRV_SOS8

39

*DATA DRIVER

8

27

45

D12A-D13C

DDR-IO

53

CLKU6(+)

IC9602

C24

TO C24

IC9505

43

2

CSH

55

5

CPH

55

39

Q9305

68

CLKU6(+)

SCAN CONTORL

13

56

D23C

SUSTAIN CONTROL

CLR

U2

IC9402

U16A

D35

U17B

+5V DET

D11C

13

22

11

68

P+5V

8

PCK

8

38

59

CONTROL

44

56

5

35

D32

41

C60

TO C60

IC9603

(D16A,D17A

D17C)

D6A-D7C

U17A

14

23

52

12

R

PCU2

DATA 30Bit

53

ODEU2

7

P+5V

D9C

DATA

CLRD5

61

67

DATA 4Bit

I/F

61

48

10bit

CLKD7(-)

7

9

DDR-IO

PROCESSOR

8

D34

43

59

36

38

D20A

SC_SOS2

(U16A

U17A)

6

27

P+5V

2

D14A-D14C

U14C

35

U20A

P+3.3V

CLKU3(-)

40

59

SC_SOS1

SID

22

U19C

26

U14B

DATA 6bit

5

CLKD0(+)

PCU1

10

PCU1

USH

PCU2

39.5MHz

66

24

27

D16A

Q9304

CEL2

NOISE NR

21

CLKU4(+)

2

54

DDR-DRAM

68

2

67

23

CEL

XRST

CEH

64

Q9302

10

17

8

DET

U26C

9

DATA 13bit

P+2.5V

6

39

49

OCK

RESET

D28B,D28C

LED6

30

OCK

CONT

46

67

D27C,D28A

34

U29B

CONT

13

61

U26B

UMH

IC9504

10

LED5

U0A

42

24

DET

66

UEH

CLKU1(-)

19

CLKU5(-)

37

1

U2A

CLKD6(+)

14

D29A-D29C

51

+5V

D18A-D19C

13

17

B

D31

P+3.3V

38

45

18

CLRD6

5

DATA PROCESS

+5V DET

31

PCD6

(D22A

D31C)

P+5V

9

15

IIC

ODED5

D0A-D1C

P+2.5V

54

G

CLKU2(+)

48

30

16

CML

6

DATA 30Bit

IC9304

CLKU5(-)

MPEG

D15C

33

+5V DET

P+5V

50

RST

48

P+5V

32

D15A,D15B

3

DATA 4Bit

20

CLKD0(+)

60

3

DATA 30Bit

12

PCK

9

UEH

CLKU7(-)

59

U22A

(U17B

U21C)

42

CLKU4(+)

DATA 4Bit

10

46

D16B,D16C

3.3V->5V

9

D26A-D26C

DET

58

CLRD5

CLKU6(+)

R

U24A

31

+5V

1

14

D21C

5

50

47

CLKU2(+)

D17A-D17C

RESET

U21C

30

(U0A

U9C)

60MHz

LED6

PLL SYNTHESIZER

(D0A

D9C)

B

IC9301

C10

TO C10

66

66

52

HD,VD

12

P+5V

X9200

30

P+5V

CLR

U1

D22A

28

U28A

19

10

CLOCK

67

USH

+5V

ODEU2

CLKD4(+)

CLKU1(-)

D14A-D14C

37

41

U27C

30

27

U10A

D5A-D5C

CLKD3(-)

TO SC20

USL

33.6MHz

3.3V->5V

CLKD6(+)

CLKD1(-)

66

10bit

DATA 30Bit

DATA 14Bit

49

C54

TO C54

ODED6

ODED6

*S/P CONV.

68

41

ODED5

P+5V

28

LEDU1

U4B

U12A

DATA 14Bit

64

19

CLKD2(+)

CLKD2(+)

43

DATA

11

OCK

8

67

59

57

C55

TO C55

50

OCK

35

D33

XRST

P+5V

SCSU

34

U9C

D30A-D31C

(U22A

U31C)

67

D8A

P+2.5V

PCK

45

D4B,D4C

P+5V

55

33

8

CLKD7(-)

29

31

PDP PANEL SIGNAL PROCESSOR

CL

D10A

(D14A

D14C,D15C)

P+5V

60

CLKU5(-)

+5V

64

59

17

60

VDD

33

DATA

C25

TO C25

+5V DET

128Mbit

P+5V

2

33.6MHz

32Mbit

59

D24A-D24C

3

PCD5

18

U7A

LED5

36

52

63

29

P+5V

P+1.2V

IC9401

11

50

64

LEDU1

9

31

CMH

U17A

45

61

46

31

CLKD4(+)

27

60MHz

D27A,D27B

39

D15C,D16A

66

ADR

19

16

37

1

(U14C

U15C)

3

CLKU7(-)

51

68

IC9503

D25A-D25C

DATA 4Bit

41

20

P+1.2V

DET

47

16

60MHz

67

P+5V

2

U15C

34

14

Q9303

P+5V

SUB FIELD

61

20MHz

2

8

LEU2

DDR-DRAM

G

58

DET

CLKD3(-)

64

6

67

10

IIC

3

DATA 14Bit

26

59

+5V DET

10bit

U7B

BUS SWITCH

P+5V

U4C

37

3.3V->5V

CLR

U2

2

FLASH MEMORY

64

DATA CONTROL

6bit

40

2

49

39

U14C

D3C,D4A

USL

24

CLKU7(-)

U31C

CSL

P+5V

11

CLKU0(+)

CLKD5(-)

58

1

36

+5V

53

38

I/F

30

CLKU0(+)

P+5V

32

FLASH

43

P+5V

42

HD,VD

68

U23C

ODEU1

57

CLKU4(+)

3

P+5V

39

FLASH

32

(D10A

D15B)

CLK OUT

RESET

62

ODEU1

10bit

58

UML

28

CONT

12

DET

*SF TABLE CONV.

45

NUEL

51

14

ADR

15

8

32

RESET

23

60

28

9

3

U1C

D36

3.3V->5V

SIU

11

24

43

U11C

4

55

PCK

IC9300

D3A,D3B

67

CLK OUT

20

20

PCD6

21

18

+5V

Q9301

39

24

128Mbit

18

30

(U10A

U14B)

D20

1

PCD5

D2A-D2C

10

CLRD6

19

10

63

58

P+3.3V

56

CLKU0(+)

5

38

21

42

17

PLASMA AI PROCESSOR

D FORMAT CONVERTER,

LEVEL SHIFT

LEVEL SHIFT

LEVEL SHIFT

LEVEL SHIFT

PROCESSOR

CLOCK

*CONTOUR CORRE.

PDP PANEL SIGNAL PROCESSOR

*S/P CONV.

*SF TABLE CONV.

SUB FIELD

NOISE NR

*DATA DRIVER

*CONTOUR CORRE.

DATA PROCESS

MPEG

TH-50PY700F/P, PZ700B/E

D-Board (2 of 2) Block Diagram

TH-50PY700F/P, PZ700B/E

D-Board (2 of 2) Block Diagram

16

17

18

19

20

21

22

1

3

2

4

5

6

7

8

9

10

11

12

13

14

15

TH-50PZ700B / TH-50PZ700E / TH-50PY700F / TH-50PY700P

122

Содержание TH-50PY700P

Страница 5: ...1 Applicable signals 5 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 22: ...8 Location of Lead Wiring 8 1 Lead of Wiring 1 22 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 23: ...8 2 Lead of Wiring 2 23 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 24: ...8 3 Lead of Wiring 3 24 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 28: ...9 4 No Picture 28 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 35: ...11 4 Adjustment Volume Location 11 5 Test Point Location 35 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 40: ...40 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 75: ...15 Schematic and Block Diagram 15 1 Schematic Diagram Note TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P 75 ...

Страница 157: ...16 Exploded Views Replacement Parts List 16 1 Exploded Views 157 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 158: ...16 2 Packing Exploded Views 1 158 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 159: ...16 3 Packing Exploded Views 2 159 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 160: ...16 4 Packing Exploded Views 3 160 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...

Страница 161: ...16 5 Replacement Parts List Notes 161 TH 50PZ700B TH 50PZ700E TH 50PY700F TH 50PY700P ...