S-53

1

4

8

58

59

57

62

63

60

61

53

51

49

50

52

55

56

54

26

25

28

27

23

21

19

18

20

22

24

32

30

29

31

3

64

2

15

11

13

12

10

14

16

17

9

5

4

8

6

7

46

44

42

40

38

36

34

33

35

37

39

41

43

45

47

IC57001

MN101C77CPD

X_SW3R3V

SD_L

NP_MUTE

FL_ON_H

JC_P_ON_H

P_STANBY_H

FAN_PWR

H

D

M

I

_

C

O

N

T

DR_P_ON_H

P_SAVE_L

HDMI_P_ON_H

OFF_MUTE

SD_BOOT

XBPRST

V

O

U

T

_

M

U

T

E

_

L

0.01

C57019

16V

C

5

7

0

1

0

0

.

0

1

1

6

V

C

5

7

0

1

2

0

.

0

1

1

6

V

C

5

7

0

1

3

0

.

0

1

1

6

V

C57008

0.1

10V

C57009 0.1

10V

C

5

7

0

2

0

F

1

H

1

A

1

0

5

A

0

2

8

1

0

V

C57017

ECJ1VB1C104K

16V

C

5

7

0

1

8

F

1

H

1

A

1

0

5

A

0

2

8

1

0

V

C

5

7

0

2

2

0

.

0

1

1

6

V

C57011

0.1

10V

C

5

7

0

2

1

F

1

H

1

A

1

0

5

A

0

2

8

1

0

V

C

5

7

0

0

2

E

C

J

1

V

B

1

H

1

0

3

K

5

0

V

ECJ1VB1C104K

C57003

1

6

V

100P

C57014

50V

C

5

7

0

1

5

0

.

0

1

1

6

V

0

.

0

1

C

5

7

0

1

6

1

6

V

C57001

0.1

1

0

V

27P

C57004

50V

27P

C57005

50V

0

R57030

R

5

7

0

0

7

0

R

5

7

0

0

8

0

R57020

47K

$

(

1

0

0

)

R

5

7

0

2

1

R57022

$(100)

R57023

$(100)

8200[D]

R57024

8200[D]

R57025

8200[D]

R57026

R57029

$(4700)

$

(

1

0

K

)

R

5

7

0

3

2

10K

R57031

1

0

0

R

5

7

0

3

5

R

5

7

0

3

6

4

7

K

4

7

K

R

5

7

0

4

4

R57045

47K

4

7

K

R

5

7

0

4

6

R

5

7

0

4

8

$

(

2

2

0

0

)

$(5600)

R57049

R

5

7

0

5

0

4

7

K

R

5

7

0

5

1

2

4

0

0

[

D

]

R57052

2200[D]

R57057

100

R57058

100

R57060

82K

$

(

2

2

0

K

)

R

5

7

0

6

1

R57062

4700

R57063

100[22]

R57043

10K

R57009

10K

30K

R57011

820

R57010

R57059

100

$(0)

R57033

$(10K)

R57076

0

R57075

R57003

47

R

5

7

0

1

4

1

0

0

[

1

8

]

R

5

7

0

1

2

1

0

0

[

1

8

]

R

5

7

0

1

3

1

0

0

[

1

8

]

R

5

7

0

8

1

$

(

0

)

[

1

8

]

0

[

1

8

]

R

5

7

0

1

5

1

0

0

[

1

8

]

R

5

7

0

1

6

1

0

0

[

1

8

]

R

5

7

0

1

7

1

0

0

[

1

8

]

R

5

7

0

1

8

0[18]

R57077

R57080

0

R57027

470

R57079

*

*

R

5

7

0

3

9

*

R

5

7

0

7

1

*

R57042

*

R

5

7

0

4

1

*

R57038

R

5

7

0

7

3

*

R

5

7

0

3

7

*

R57040 *

DGND

5

4

3

2

1

IC57002

C0EBD0000245

5

4

3

2

1

IC57006

C0CBCYY00001

5

4

3

2

1

IC57005

C0EBK0000206

5

2

6

1

3

4

$[B1CFGD000003]

IC57003

PW_GOOD_H

FAN_LOCK

X_SW13V

BP_STATE

ST_D3R3V

XFWE

H

D

M

I

_

M

O

N

I

X_SW5R8V

1

5

6

3

2

4

$[K1KA06AA0083]

P57003

CL57007

CL57014

C

L

5

7

0

1

5

C

L

5

7

0

1

6

C

L

5

7

0

1

7

C

L

5

7

0

2

2

C

L

5

7

0

2

4

C

L

5

7

0

3

0

C

L

5

7

0

2

3

CKL2

CKL1

CKL3

CKF2

CKF1

CKF4

CKF3

CKF5 CKF7

CKF9

CKF10

CKF8

CKF6

CL57038

CL57052

C

L

5

7

0

5

7

C

L

5

7

0

6

3

CL57028

CL57026

CL57012

CL57041

C

L

5

7

0

5

0

CL57004

Q

5

7

0

0

2

$

[

2

S

D

0

6

0

1

A

0

L

]

B1ABMF000020

Q57001

Q57004

2SD1819K0L

QR57001

$[UNR5111J0L]

UNR51ALJ0L

QR57003

QR57006

*

1

3

2

D57001

B0ADCH000007

D57003

$[B0JCCE000002]

D57004

$[B0ACDJ000007]

D57002

$[B0ACDJ000007]

2

1

3

4

6

8

7

5

C

0

A

B

B

A

0

0

0

1

6

8

I

C

5

7

0

0

4

QR57002

$[B1GBCFNN0041]

QR57004

UNR52A3J0L

QR57007

*

1

8

6

4

2

3

5

7

9

1

0

K

1

K

B

1

0

B

0

0

0

4

5

P

5

7

0

0

1

1

2

3

G

1

G

2

P57002

$[K1KA03AA0083]

J0JGC0000020

LB57001

FL57001

4

2

6

8

5

7

1

3

RX57002

D1H84704A024

4

2

6

8

5

7

1

3

D1H84704A024

RX57001

4

2

6

8

5

7

1

3

D1H83324A024

RX57003

4

2

6

8

5

7

1

3

D1H83324A024

RX57004

U34

U33

V30

V32

T32

T33

X57001

H0J100500035

Q57003

$[2SB0709A0L]

G

_

R

E

M

O

C

O

N

_

A

G_SBMTP_A

G_SCLK_A

G_SBPTM_A

G

_

S

B

P

T

M

_

B

G_SCLK_B

G_SBPTM_C

G_SBMTP_B

G_FL_TXD_A

G_FL_CLK_A

G_REMOCON_B

(ROHM RB500V)

(TOSHIBA 1SS352)

DR_P_ON_H

VPP(5V)

10MHz_OUT

VDD(3.3V)

S

Y

S

_

P

F

A

I

L

[

L

]

FANLOCK

V

R

E

F

-

F

A

N

_

D

C

X

I

N

T

M

_

O

U

T

X

I

N

T

P

_

O

U

T

H

D

M

I

_

M

O

N

I

(

C

E

C

_

I

N

)

X

M

P

R

E

Q

[

T

B

U

S

]

H

D

M

I

_

C

E

C

_

O

U

T

X

I

N

T

M

[

T

B

U

S

]

R

E

M

O

C

O

N

R

E

M

O

C

O

N

P

F

A

I

L

[

L

]

UARTM2P/TBUS_RXD

32.768KHz_IN

10MHz_IN

VSS

[35]DWIRE_DATA

[36]DWIRE_CLK

TEST2[H]

RESET

MMOD

UARTP2M/TBUS_TXD

32.768KHz_OUT

VOUT

GND

GND

GND

G

N

D

G

N

D

CN

VIN

ON

or

or

or

or

or

or

or

or

KISYU1

NP_MUTE

SD_L

VREF

[1]KEYIN1_OP_CL

[2]KEYIN2

[3]KEYIN3_POWER

P_STANDBY_H

KISYU3

KISYU2

P

_

S

A

V

E

_

L

D

R

_

P

F

A

I

L

[

L

]

1

2

5

0

H

z

S

T

A

N

D

B

Y

_

L

E

D

VO

VO

V

O

DH

DH

D

H

D

H

DH

DN

DN

DN

DN

DN

DN

DN

DN

DN

DN

DN

DN

G

2

G

1

S

2

D

2

S

1

D

1

[17]TBUS_CLK

[18]FL_TXD

[20]FL_CLK

[21]FL_CS[L]

AI

AI

AI

AI

NC

VDD

OUT

BP

BP

SW_UART

XRESET

MAX RD

3R3V

MAX TD

(TO JIGU)

FL_ON_H

H

D

M

I

_

P

_

O

N

[

H

]

PE

PE

ET

V

+

A

+

I

N

A

O

U

T

A

-

I

N

B

-

I

N

B

+

I

N

B

O

U

T

These parts are

L_SPSAVE

D

G

N

D

U

A

R

T

_

R

E

Q

_

H

U

A

R

T

_

R

E

Q

_

H

X

_

S

W

3

R

3

V

K

E

Y

2

K

E

Y

1

K

E

Y

3

F

L

_

C

L

K

F

L

_

C

S

F

L

_

T

X

D

C

E

N

T

E

R

_

L

E

D

C

E

N

T

E

R

_

L

E

D

Timer Serial I/F

BP1

arranged near IC57001.

L

E

D

_

S

T

A

N

D

B

Y

FL_WAKEUP

[34]NC_GND

N

C

_

G

N

D

N

C

_

G

N

D

S

D

_

B

O

O

T

O

F

F

_

M

U

T

E

[49]JC_P_ON[H]

[51]XRES_BP

[33]NC_GND

FL_DCDC(NC_OPEN)

B

P

_

S

T

A

T

E

[19]NC_GND

V

_

O

U

T

_

M

U

T

E

_

H

[50]P_SAVE_H

Confidential

Until

2009/1/19

Modify Category

1

2

3

4

5

6

7

8

9

10

11

Variation

Type

BD80GN1

L

BD60GN1,GC1,GA1,GK1

K

BD80EG1,EB1

J

BD60EG1,EB1,EF1,EE1

H

BD80P1,PC1

G

BD60P1,PC1

F

BD60

E

BD80EG,EB

D

BD60EG,EB,EF,EE

C

BD80P,PC,GN

B

BD60P,PC,PU,GN,GC,GA,GK

A

VariationCategory

IC51001

QR57006

QR57007

R57037

R57038

R57039

R57040

R57041

R57042

R57071

R57073

R57079

A

B

C

D

E

F

G

H

J

K

L

$(0)

0

$(0)

0

$(0)

$(0)

0

$(0)

0

$(0)

0

$(47K)

$(47K)

$(47K)

$(47K)

$(47K)

$(47K)

$(47K)

$(47K)

$(47K)

$(47K)

$(47K)

47K

47K

47K

47K

47K

47K

47K

47K

47K

47K

47K

$(10K)

$(10K)

$(10K)

$(10K)

10K

$(10K)

$(10K)

$(10K)

$(10K)

$(10K)

$(10K)

0

0

0

0

$(10K)

0

0

0

0

0

0

$(10K)

$(10K)

$(10K)

$(10K)

10K

$(10K)

$(10K)

$(10K)

$(10K)

$(10K)

$(10K)

0

0

0

0

$(10K)

0

0

0

0

0

0

$(10K)

$(10K)

10K

10K

$(10K)

$(10K)

$(10K)

10K

10K

$(10K)

$(10K)

0

0

$(0)

$(0)

0

0

0

$(0)

$(0)

0

0

$[UNR52A1J0L]

UNR52A1J0L

│UNR5211J0L

│B1GBCFJJ0040

$[UNR52A1J0L]

UNR52A1J0L

│UNR5211J0L

│B1GBCFJJ0040

$[UNR52A1J0L]

$[UNR52A1J0L]

UNR52A1J0L

│UNR5211J0L

│B1GBCFJJ0040

$[UNR52A1J0L]

UNR52A1J0L

│UNR5211J0L

│B1GBCFJJ0040

$[UNR52A1J0L]

UNR52A1J0L

│UNR5211J0L

│B1GBCFJJ0040

$[UNR51AHJ0L]

UNR51AHJ0L

│UNR511HJ0L

│B1GDCFEJ0010

$[UNR51AHJ0L]

UNR51AHJ0L

│UNR511HJ0L

│B1GDCFEJ0010

$[UNR51AHJ0L]

$[UNR51AHJ0L]

UNR51AHJ0L

│UNR511HJ0L

│B1GDCFEJ0010

$[UNR51AHJ0L]

UNR51AHJ0L

│UNR511HJ0L

│B1GDCFEJ0010

$[UNR51AHJ0L]

UNR51AHJ0L

│UNR511HJ0L

│B1GDCFEJ0010

MN2WS0061AFF

MN2WS0061DFF

MN2WS0061DFF

MN2WS0061DFF

MN2WS0061AFF

MN2WS0061AFF

MN2WS0061DFF

MN2WS0061DFF

MN2WS0061DFF

MN2WS0061AFF

MN2WS0061DFF

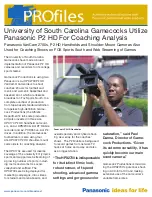

DMP-BD60/BD80GN Series

Timer Section

(Digital P.C.B.(11/12))

Schematic Diagram(TM)

DMP-BD60/BD80GN Series

Timer Section

(Digital P.C.B.(11/12))

Schematic Diagram(TM)

DMP-BD60/BD80GN Series

Timer Section

(Digital P.C.B.(11/12))

Schematic Diagram(TM)

DMP-BD60/BD80GN Series

Timer Section

(Digital P.C.B.(11/12))

Schematic Diagram(TM)

2/4

4/4

1/4

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

N

M

L

K

J

I

H

G

F

E

D

C

B

A

3/4

Содержание DMP-BD60GN

Страница 7: ...7 4 Specifications ...

Страница 8: ...8 ...

Страница 20: ...20 7 2 Adjustment of BDP Digital P C B Module 7 2 1 Repair Flowchart ...

Страница 21: ...21 7 2 2 Distinction Analysis 7 2 2 1 Distinction Analysis Flowchart ...