Appendix A

Specifications

PCI-6023E/6024E/6025E User Manual

A-4

©

National Instruments Corporation

Dynamic Characteristics

Bandwidth

Settling time for full scale step ...............5

µ

s max to ±1.0 LSB accuracy

System noise (LSBrms, not including quantization)

Crosstalk .................................................–60 dB, DC to 100 kHz

Stability

Recommended warm-up time.................15 min.

Offset temperature coefficient

Pregain.............................................±15 µV/°C

Postgain ...........................................±240 µV/°C

Gain temperature coefficient ..................±20 ppm/°C

Analog Output

♦

(PCI-6024E and PCI-6025E only)

Output Characteristics

Number of channels................................2 voltage

Resolution ...............................................12 bits, 1 in 4,096

Max update rate .....................................100 kHz, system dependent

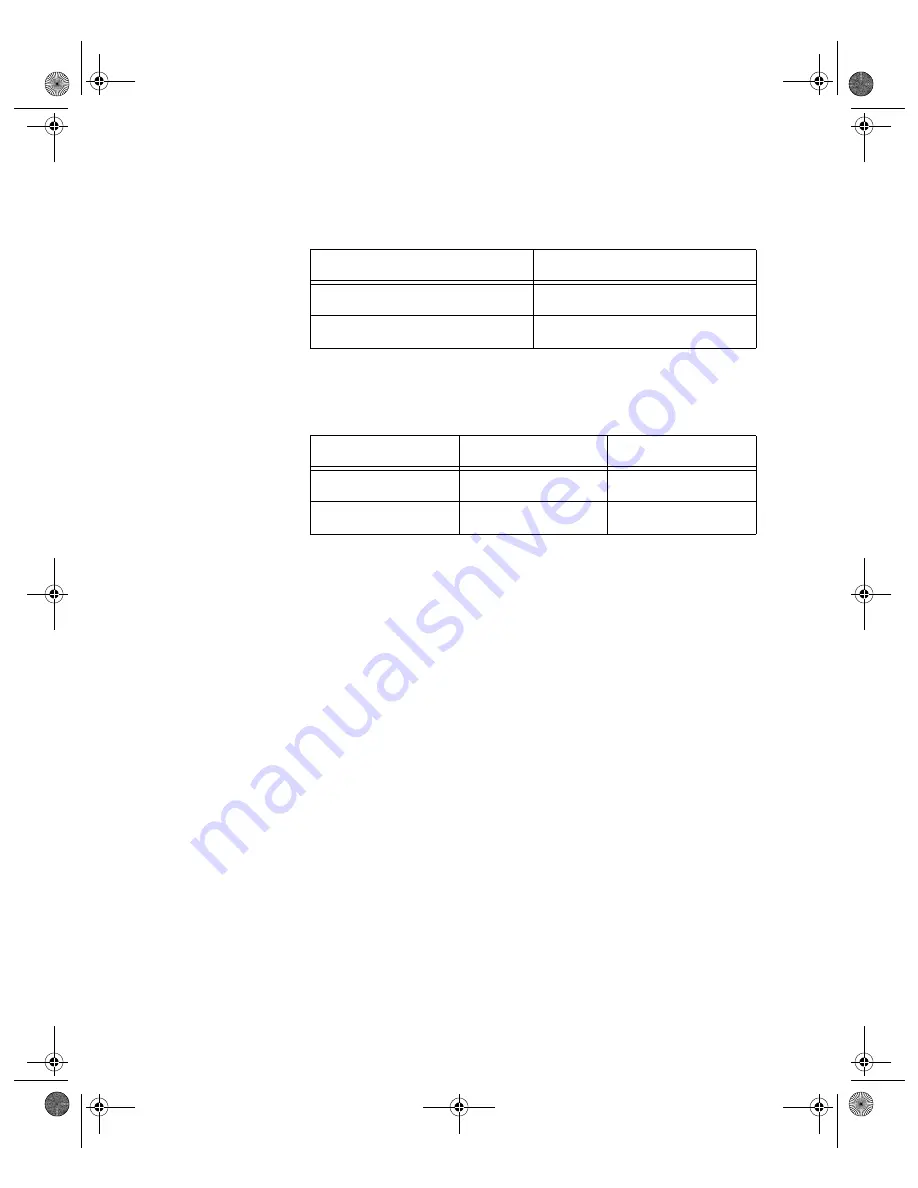

Signal

Bandwidth

Small (–3 dB)

500 kHz

Large (1% THD)

225 kHz

Gain

Dither Off

Dither On

0.5 to 10

0.1

0.6

100

0.7

0.8

PCI.book Page 4 Wednesday, September 16, 1998 9:09 AM