©

National Instruments Corporation

3-1

PCI-4451/4452/4453/4454 User Manual

3

Hardware Overview

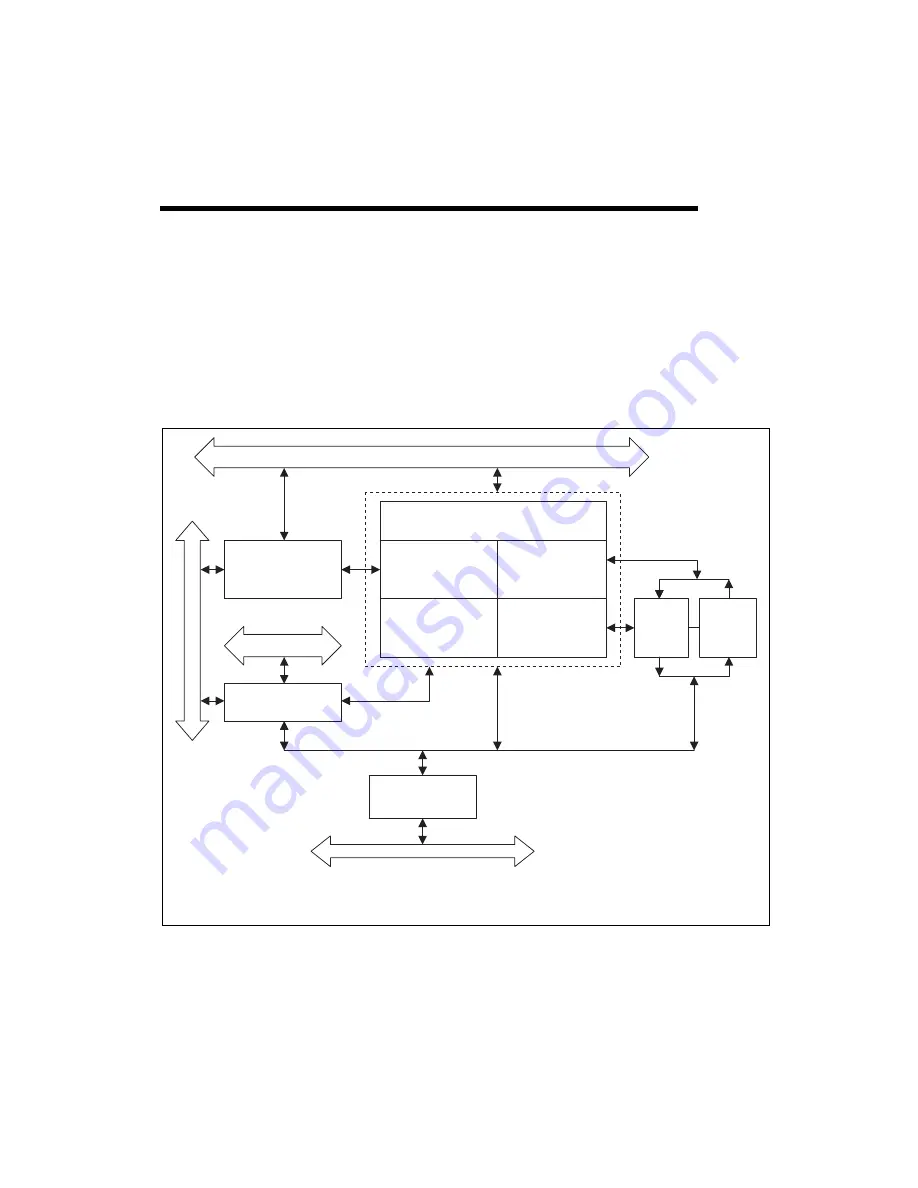

This chapter presents an overview of the hardware functions on your

PCI-445X. Figure 3-1 shows a block diagram of the digital functions. The

analog function block diagrams are shown in Figures 3-2 and 3-3. The

digital and analog function blocks connect through the analog mezzanine

bus.

Figure 3-1.

Digital Function Block Diagram

Direct Digital

Synthesis

Clock Generator

DAQ-STC

AI FIFO

MITE

PCI Controller

PCI Bus

AO FIFO

†

Parallel <–> Serial

Converter

FIFO and DMA

Control

General Control

Functions

Clock Control

R

TSI Bus

Digital I/O Bus

††

Analog Mezzanine Bus (to Analog Section)

Analog Mezzanine Control

†

PCI-4451/4453 only

††

PCI-4451/4452 only