Chapter 4 Signal Connections

National Instruments Corporation

4-53

AT-MIO/AI E Series User Manual

Timing Specifications for Digital I/O Ports A, B, and C

♦

AT-MIO-16DE-10 only

In addition to its function as a digital I/O port, digital port C,

PC<0..7>, can also be used for handshaking when performing data

transfers with ports A and B. The signals assigned to port C depend

on the mode in which it is programmed. In mode 0, port C is

considered two 4-bit I/O ports. In modes 1 and 2, port C is used for

status and handshaking signals with two or three additional I/O

bits. Table 4-5 summarizes the signal assignments of port C for

each programmable mode.

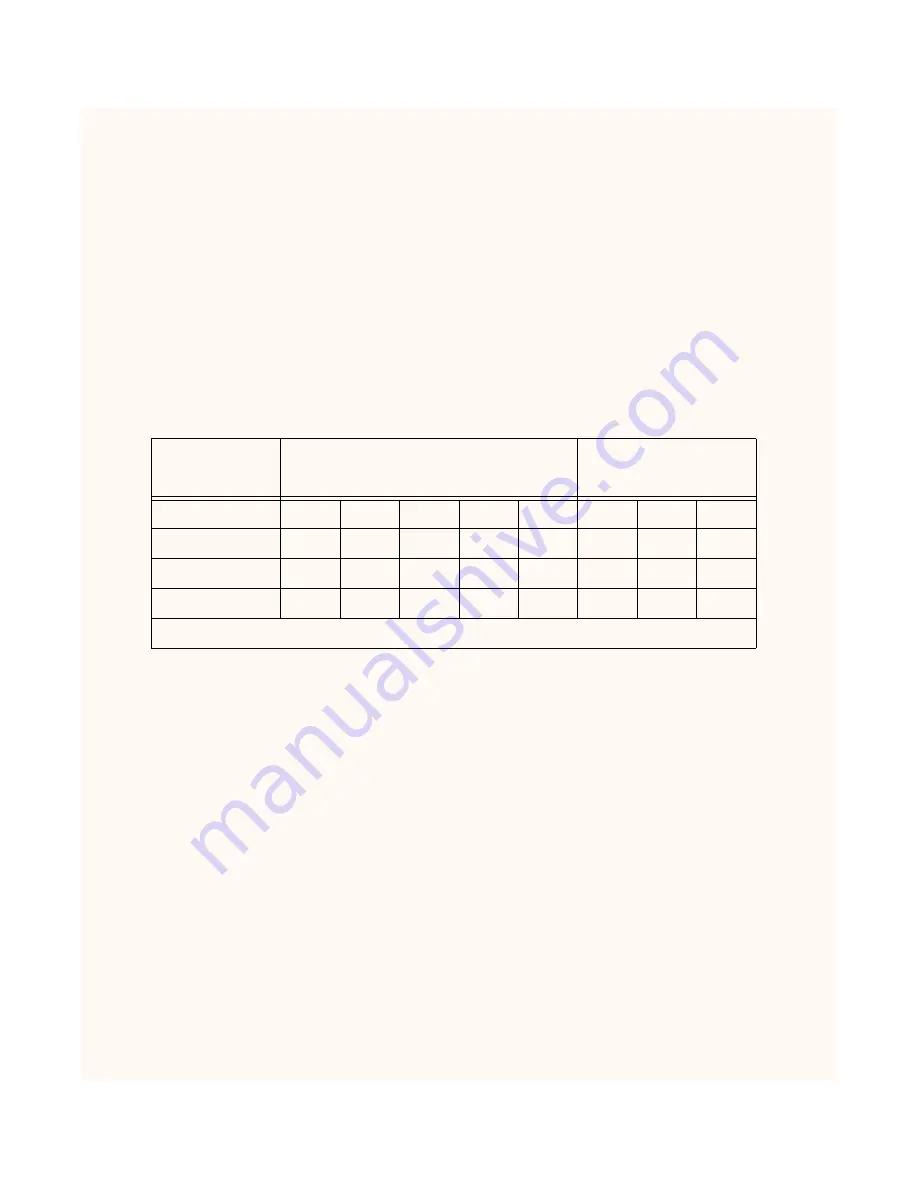

Table 4-5.

Port C Signal Assignments

Programming

Mode

Group A

Group B

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PC0

Mode 0

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Mode 1 Input

I/O

I/O

IBFA

STBA*

INTRA

STBB*

IBFBB

INTRB

Mode 1 Output

OBFA*

ACKA*

I/O

I/O

INTRA

ACKB*

OBFB*

INTRB

Mode 2

OBFA*

ACKA*

IBFA

STBA*

INTRA

I/O

I/O

I/O

* Indicates that the signal is active low.