Chapter 4

Signal Connections

©

National Instruments Corporation

4-41

As an output, the WFTRIG signal reflects the trigger that initiates

waveform generation. This is true even if the waveform generation is

externally triggered by another PFI. The output is an active high pulse with

a pulse width of 50 to 100 ns. This output is set to high impedance at

startup.

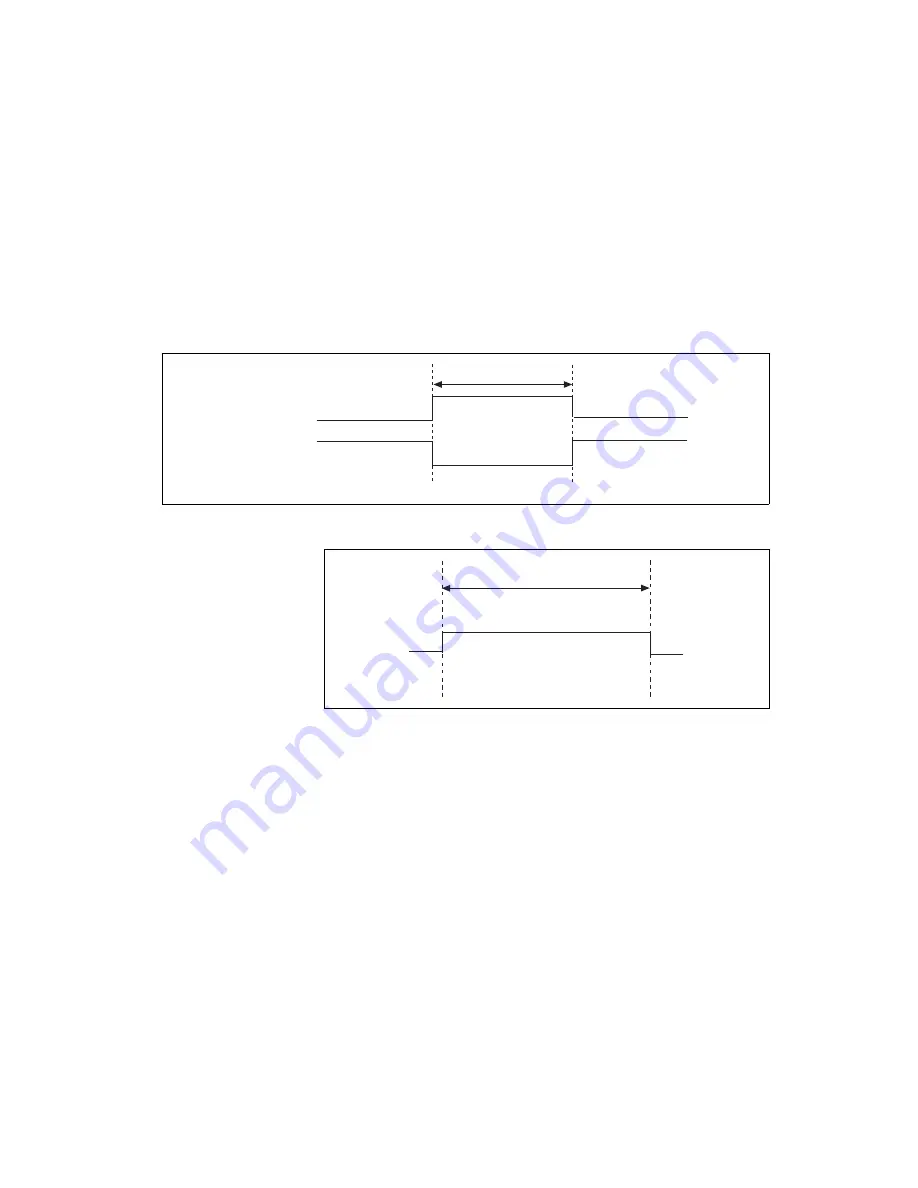

Figures 4-30 and 4-31 show the input and output timing requirements for

the WFTRIG signal.

Figure 4-30.

WFTRIG Input Signal Timing

Figure 4-31.

WFTRIG Output Signal Timing

UPDATE* Signal

Any PFI pin can externally input the UPDATE* signal, which is available

as an output on the PFI5/UPDATE* pin.

As an input, the UPDATE* signal is configured in the edge-detection mode.

You can select any PFI pin as the source for UPDATE* and configure the

polarity selection for either rising or falling edge. The selected edge of the

UPDATE* signal updates the outputs of the DACs. In order to use

UPDATE*, you must set the DACs to posted-update mode.

Rising-Edge

Polarity

Falling-Edge

Polarity

t

w

t

w

= 10 ns minimum

t

w

t

w

= 50-100 ns